2016-10: Project->shelved. I got a couple of ready-made DDS that are more flexible (yet more awkward to use). No need to reinvent this wheel...

I thought, why buy a frequency converter board ?

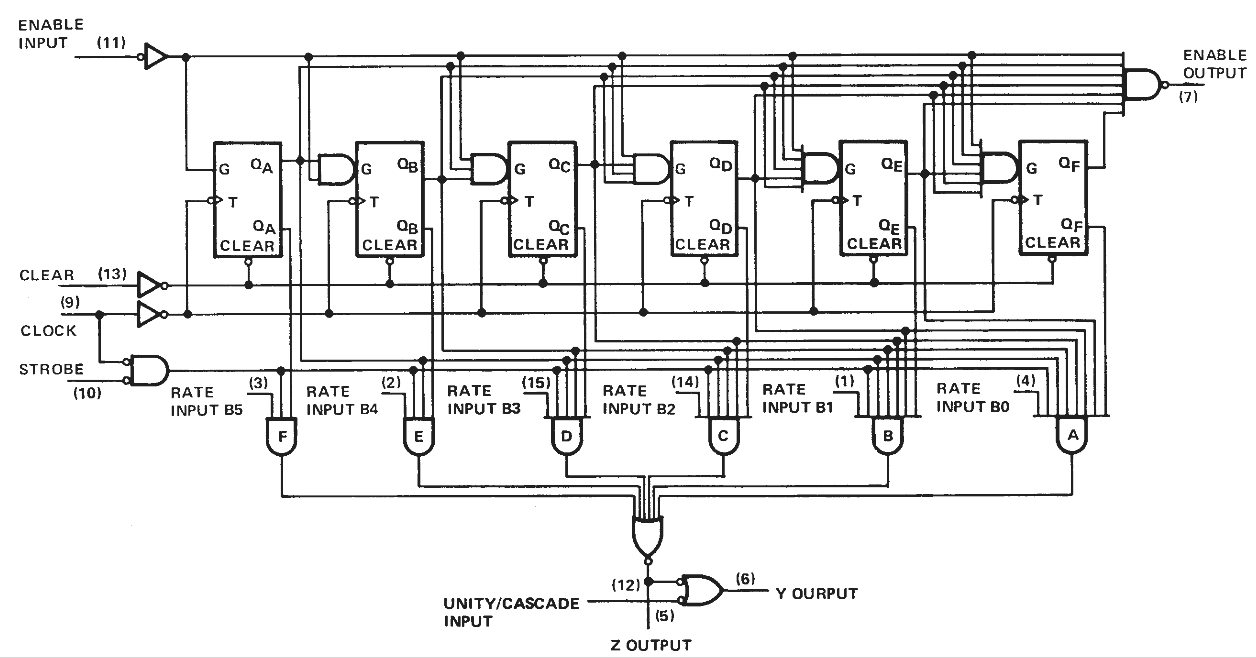

I promise, at first, I just wanted to connect a 4017 and a couple of 4040. But when I realised I have a hammer lying around, so hey, why not.

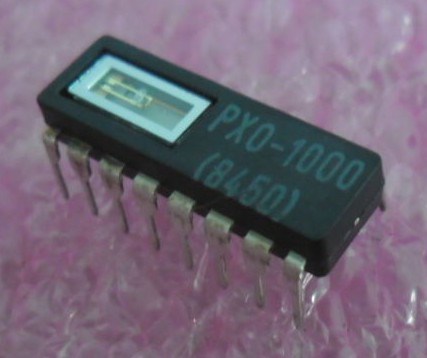

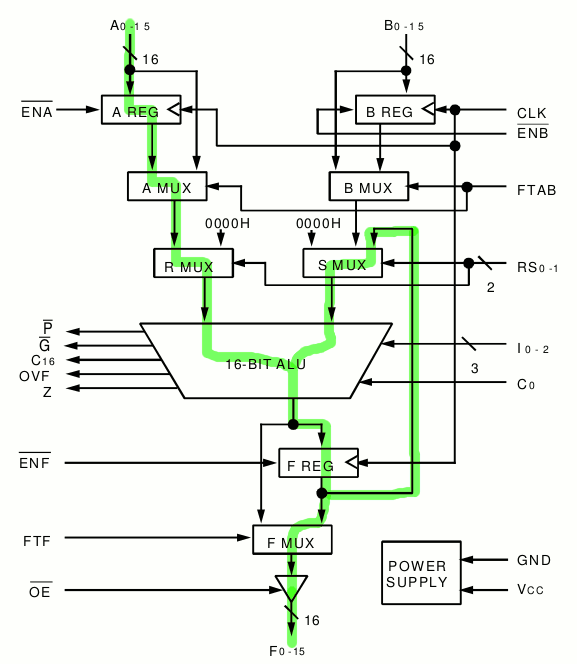

The IDT7381 is a 16-bits ALU that cost me only a few bucks and can work at 25ns (40MHz) when looping with its internal buffer. This is exactly what I first intended to do with a 74HC574 and a 74F181. Chaining to 8 bits without a normal carry output was a PITA.

Initially I wanted to use only 3V for the power supply but the 74HC4040 would not be fast enough. Bumping up the supply voltage enables me to go a bit faster so an external input is possible.

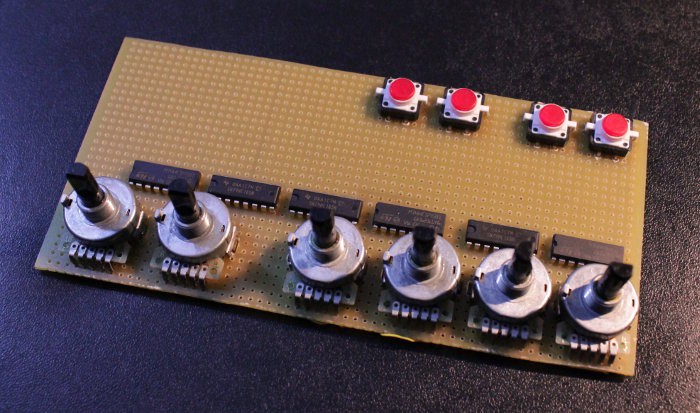

Input parameters are set with rotary buttons. They are pretty glitchy so I need to enable data with a push-button or something. The IDT7381 has a latch enable input that is meant for pipelining, this is handy in this case too !

Display is with TIL311 in the first version. They draw power, I know... but the DYPLED is not ready yet. Maybe I could even test the DYPLED with this project's interface board...

The mechanical switches can be overriden by an external digital signal, I'm adding some 74HC595, and 74HC165 to read the switch positions.

This thing borrows a LOT of ideas of, and parts from, the #Discrete YASEP and #Yet Another (Discrete) Clock

Logs:

1. Notes on using a pipelined ALU for frequency division

2. Doubling the frequency

3. Project rebirth ?

4. Alternatives

5. The (semi-aborted) front panel

Yann Guidon / YGDES

Yann Guidon / YGDES

Hah! Had no idea ALUs came like this... then did a search on digikey and... apparently all there is these days is 74-series, as I kinda thought :/