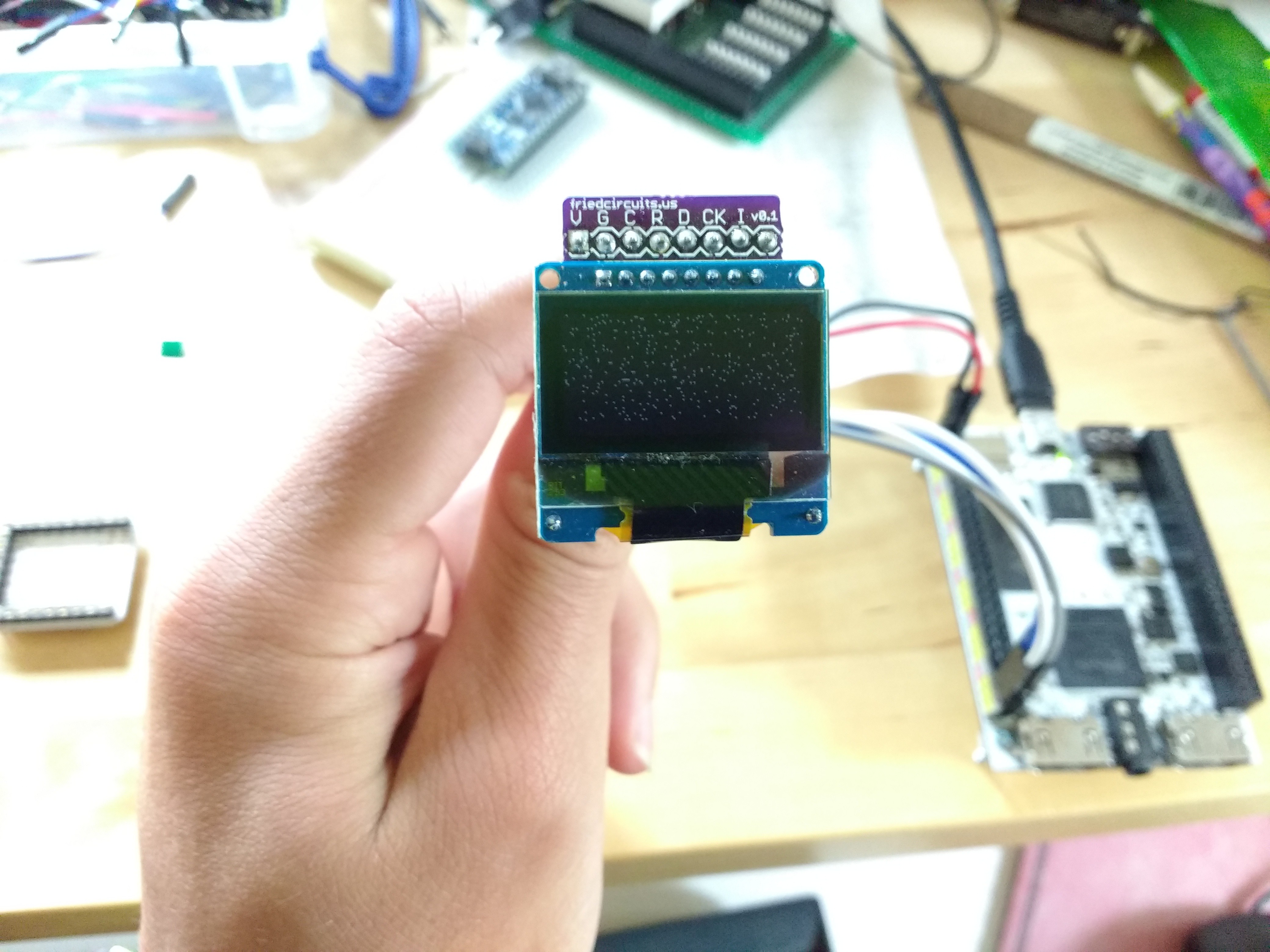

I wrote some vhdl to connect the core module to my spi module that I created, as well as some assembly code. Looking at the simulation waveform, the display should theoretically display a blank screen, but that was not the case. The clock and data are slow enough according to the ssd1306 spec sheet, but I'll try a slower clock later (the whole spi controller runs off of the divided clock, so slowing the sclk will introduce problems with the fifo which will require some redesign, otherwise I would have already done it). Even though it is far from working, it's still exciting to see pixels light up on the display. As usual, commentless :( vhdl code is up on github.

(side note: I have tested the display with an arduino, and it does work).

Picture of the display

SPI waveform

Reed Foster

Reed Foster

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.