The seller's description of this object is "FEI fe-5680b rubidium oscillator With 1pps 20mhz output ONLY/10mhz NEED to MOD" and it includes pictures showing the PCB. The "NEED to MOD" part makes it clear that the box must be opened.

The 1pps signal should be directly available on pin 5 of the HD15 connector. The only catch is that it only appears when the clock is locked. Some more practical considerations are provided in "I can't see the 1pps output!".

(I haven't see it yet so I presume I've not turned it on long enough for a lock)

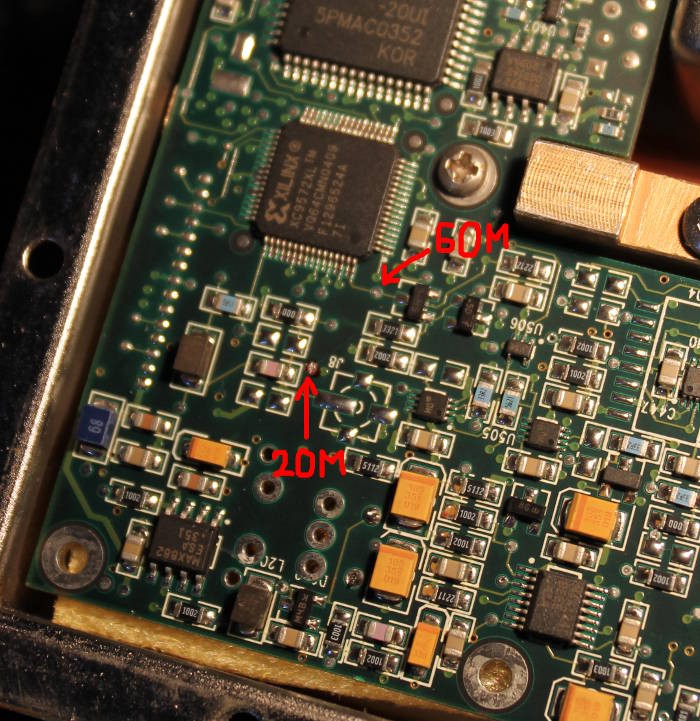

The advertised 20MHz is explained by the seller : find it on the PCB and solder a wire.

So far, so good and I've found the 20MHz as expected.

So far, so good and I've found the 20MHz as expected.

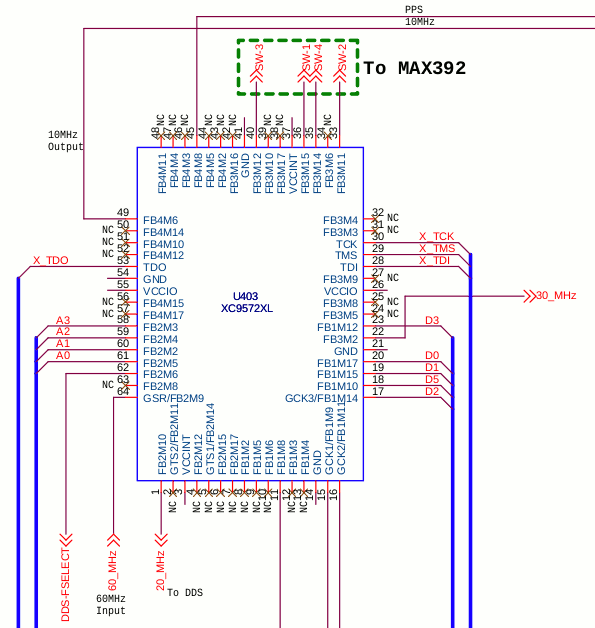

Now, somewhere (I'll probably remember the link one day) I found the schematic (somewhat reverse-engineered) of the model A. This is not model B but some similarities are striking. In particular there is the same Xilinx CPLD with those interesting signals: The CPL gets 60MHz and outputs 30MHz, 20MHz, 10MHz and 1pps.

The CPL gets 60MHz and outputs 30MHz, 20MHz, 10MHz and 1pps.

Several attempts have been made to dump the CPLD's configuration but that's not really interesting, as the lower-left corner shows the interesting part: this is the 60MHZ input (coming from the clock generator).

Is this valid for my model B?

The probe peeked at that pin and found the expected high frequency signal. Looking around, I found that this signal is available on a testing point (just like the previous 20MHz), so there is no need to hack the other side of the PCB !

I also notice something else : this signal appears to be coming from the collector/drain of a transistor, so it might be already amplified and this would reduce interference with the clocking subsystem.

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.