Currently I'm trying to jump to the last car of efabless train :)

- made a few test designs for TinyTapout that goes with efabless 130nm process as part of TT02;

- and also submitted 2 open source test designs to efabless 1st 180nm process that should go through GlobalFoundries

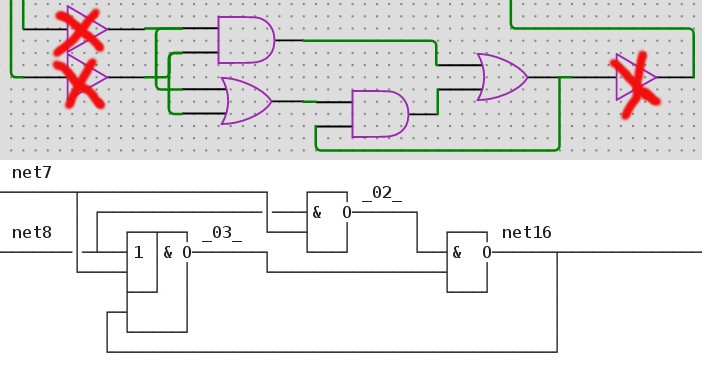

Nothing fancy, because everything is done through Verilog - you can actually draw your schematics in Wokwi but it's eventually converted to Verilog as well. Good thing is that self-made latches are translated to low level almost as is:

This is a Muller gate (or C-gate) and if it will work as intended on actual chip then it means async designs are very possible with this Yosys driven process :)

SHAOS

SHAOS

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

I'll have to wait until I can get a tapeout that provides at least 30 direct IOs, or #YGREC8 won't be possible.

I already have the ceramic chip carriers :-P but no bonding machine.

Are you sure? yes | no

GF180 provides 16 inputs and 12 outputs (without need of reprogramming of on-board microcontroller) and you always can do multiplexing :)

Are you sure? yes | no

can some of them be bidirectional ?

I'll need to know more :-P

Are you sure? yes | no

I think by re-programming of onboard RISC-V MCU you can add a few IOs and probably make some bidirectional - I need to learn more myself :)

For now I use simplest way possible - custom logic exists on the side and on-board MCU is not used.

UPDATE: Yes - all of them could be used as bidirectional! Look at

https://github.com/shaos/tiny_silicon_1/blob/main/verilog/gl/tiny_user_project.v

here 16 inputs and 12 outputs are hard-wired to be inputs and outputs, but those control bits could be driven by custom logic as well, so they could be generic IOs!

Are you sure? yes | no

output [37:0] io_oeb;

output [37:0] io_out;

input [37:0] io_in;

as you can see it's 38 IOs total, but some of them are used to control onboard MCU, so only 28 available to user by default, but it looks like user can re-program direction of them on the fly by setting/clearing io_oeb bits

This is how my 1st project connected to GP180 now:

user_module_348540666182107731 mod (

io_in[15:8],

io_out[23:16]

);

// all output enabled

assign io_oeb[23:16] = 8'b0;

https://github.com/shaos/tiny_silicon_1/blob/main/verilog/rtl/tiny_user_project.v

and very similar but more IOs in 2nd project:

user_module_350175937959035475 mod (

io_in[23:8],

io_out[35:24]

);

// all output enabled

assign io_oeb[35:24] = 8'b0;

https://github.com/shaos/tiny_silicon_2/blob/main/verilog/rtl/tiny_user_project.v

Are you sure? yes | no

GF180 designs should come in June 2023 :)

Are you sure? yes | no

nice!

Are you sure? yes | no

Hi, Matt!

Thank you for TinyTapout :)

Looking forward to participate in TT03 ;)

Are you sure? yes | no