As I said before my 1st chip is a collection of test circuits for binary, ternary and quaternary building blocks. One of that building blocks could be used directly even right now - it is ternary selector (that could connect 1 pin to any other 3 using 1-wire ternary control). SOIC16 package has only this building block wired to pins with this pinouts:

Pin 1 - Vss (negative voltage)

Pin 2 - MUST BE GROUNDED (Vss)

Pin 3 - S (analog input "select")

Pin 4 - N (analog input/output "negative")

Pin 5 - O (analog input/output "neutral")

Pin 6 - P (analog input/output "positive")

Pin 7 - C (analog output/input "common")

Pin 8 - Vdd (positive voltage)

Pin 9 - MUST BE GROUNDED (Vss)

Pin 10 - NOT CONNECTED

Pin 11 - NOT CONNECTED

Pin 12 - NOT CONNECTED

Pin 13 - NOT CONNECTED

Pin 14 - NOT CONNECTED

Pin 15 - NOT CONNECTED

Pin 16 - Vss (negative voltage)

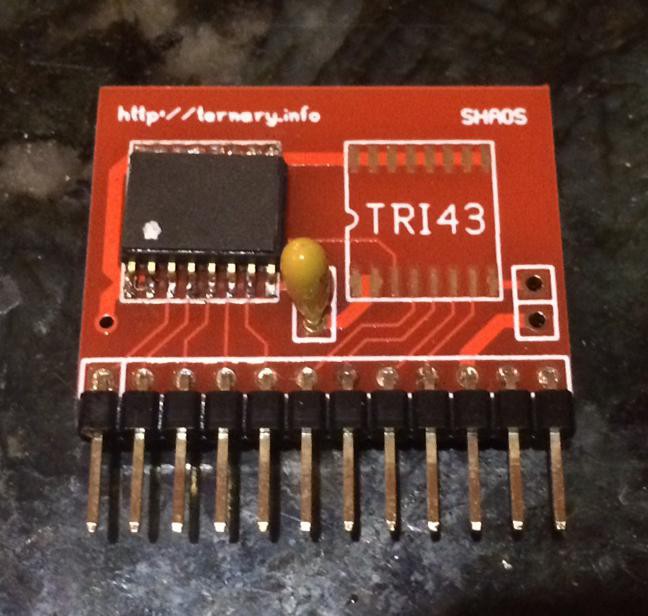

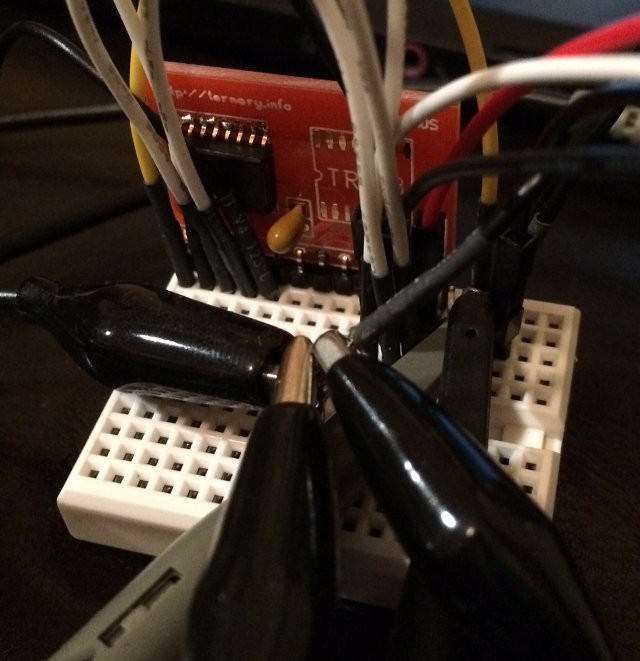

I designed a break-out board to convert SOIC to SIP (breadboard friendly):

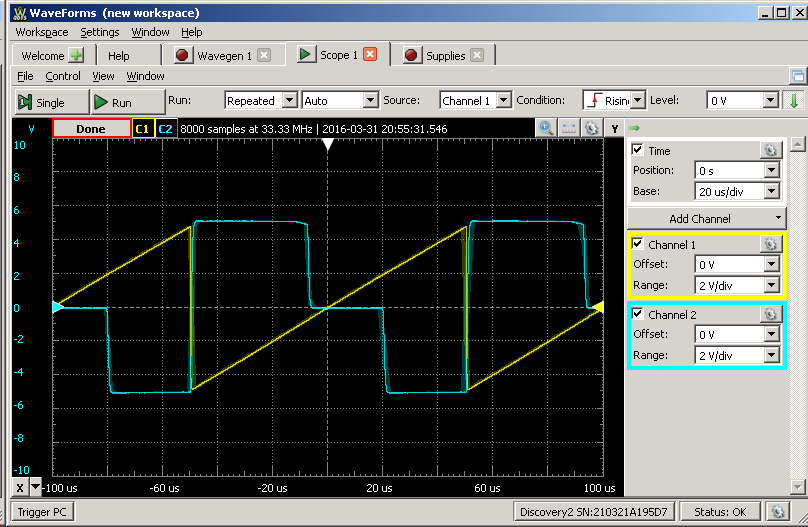

As you can see there are gaps between active zones (kind of "break-before-make" non-shorting transition) to prevent switches (X12,X13,X14) to be ON simultaneously while moving between zones (and it may cause short circuits between power lines because any of pins N,O,P could be connected to most positive or most negative voltage to implement some ternary functions using this universal ternary selector).

SHAOS

SHAOS

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.