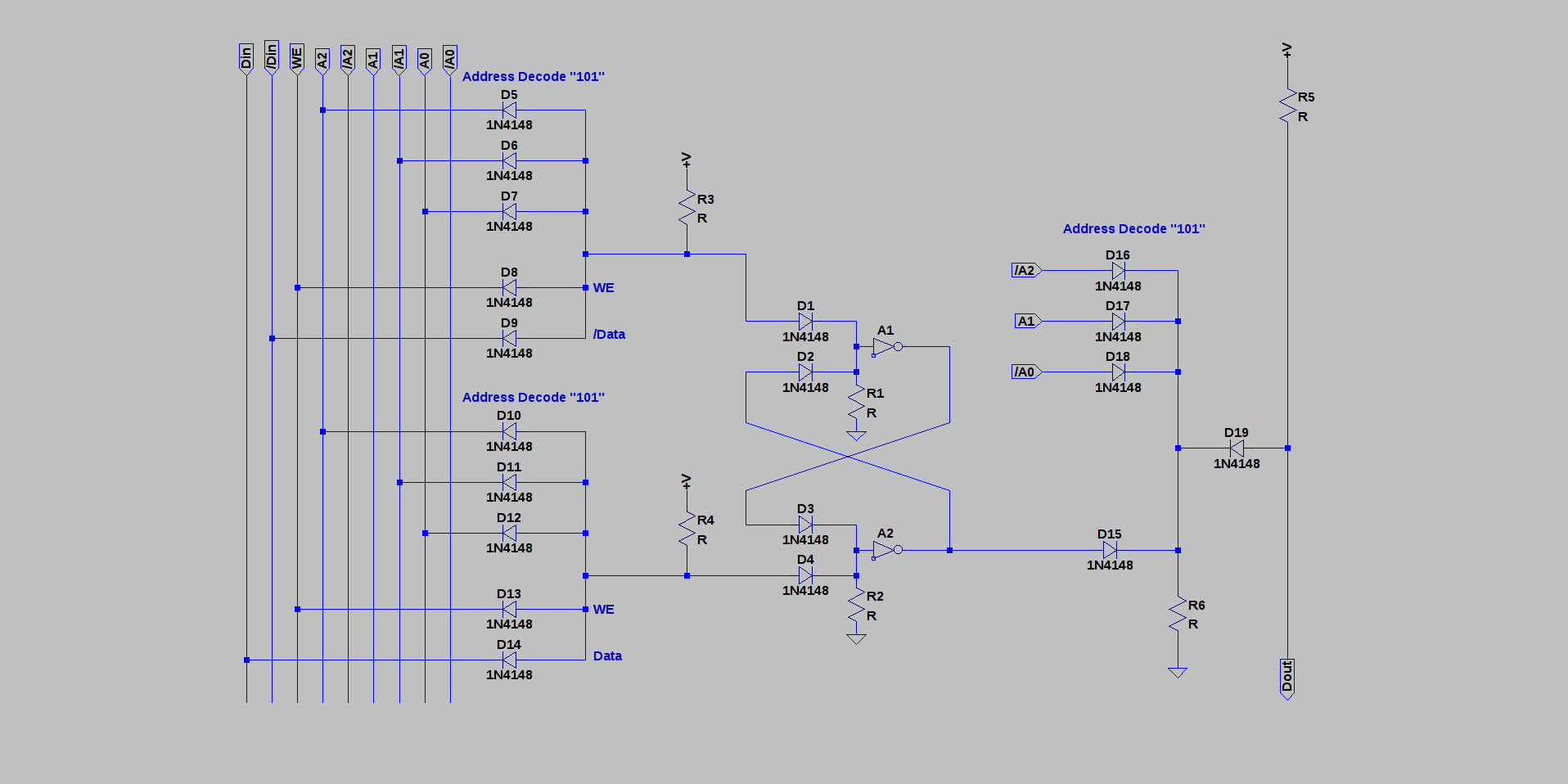

There was a mostly-diode SRAM cell design on nanocpu.org (documented here as #NanoCPU.org); I think it's undergoing some renovations at the moment, but I wanted to cite it because it was definitely what got me thinking about diode-based SRAMs again. Here's my take on the same concept - a single-bit SRAM cell using a two-inverter latch as the storage element. All the address decoding and R/W logic is done with diode AND/OR cascades - both for the input and output. This particular version decodes 3 address lines; so it would be suitable for an 8-address memory.

As with the other designs, both true and complemented address and data lines are required - this costs a few inverters, but this cost is amortized over the number of storage cells. For N address lines, this design requires 3N+10 diodes per bit (less if the latch diodes are built into NOR gates, for example). You can reduce this somewhat if you allow two levels of AND diodes; then the write address decode can be done once, reducing the number of diodes to 2N+10 per bit. This may or may not be a good trade-off depending on what you are using for inverters. I'll have to think about whether this can be made to work with DDL inverters, or if I have to use all the diodes.

Note that the output logic uses inverted levels so that it doesn't affect the latch; when I first uploaded the schematic, I had it backwards: it's an easy mistake to make. Since the latch has both true and complemented outputs available, it's easy enough to use the opposite output to drive inverted output logic.

As with the previous ideas along these lines, fan-out will limit the number of cells that can be used without buffering on the address and data lines. Even so, this seems like a decent storage architecture for a diode-only CPU. My previous thoughts had each bit of storage taking a whole DDL01 board (six gates). With this mostly-passive-diode idea, the density improves to store 3 bits per board (plus a bunch of diodes to put somewhere).

Ted Yapo

Ted Yapo

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.