As I am working on the FPGA I took a break to design the microphone modules for this project.

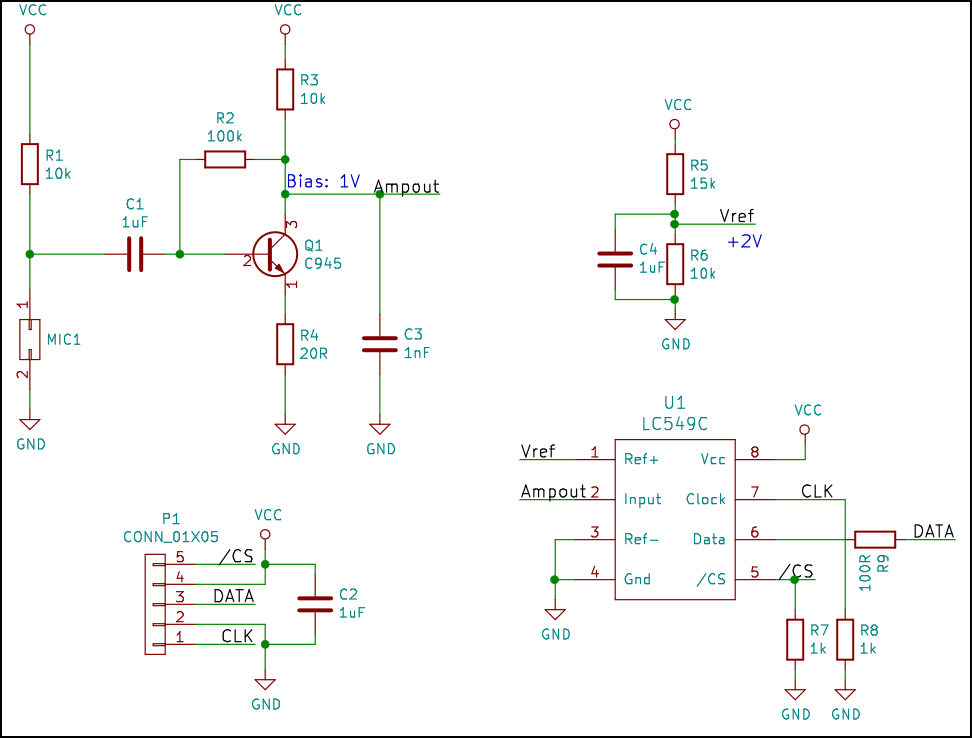

I'm unsure weather I need to impedance match the signal lines since the speed is moderate. The cable from the hub to each microphone will be a 5 pole, 600+ mm long, ribbon cable with a characteristic impedance of about 120 Ohm. All the values are preliminary and I need to breadboard this when I get the parts to test the levels.

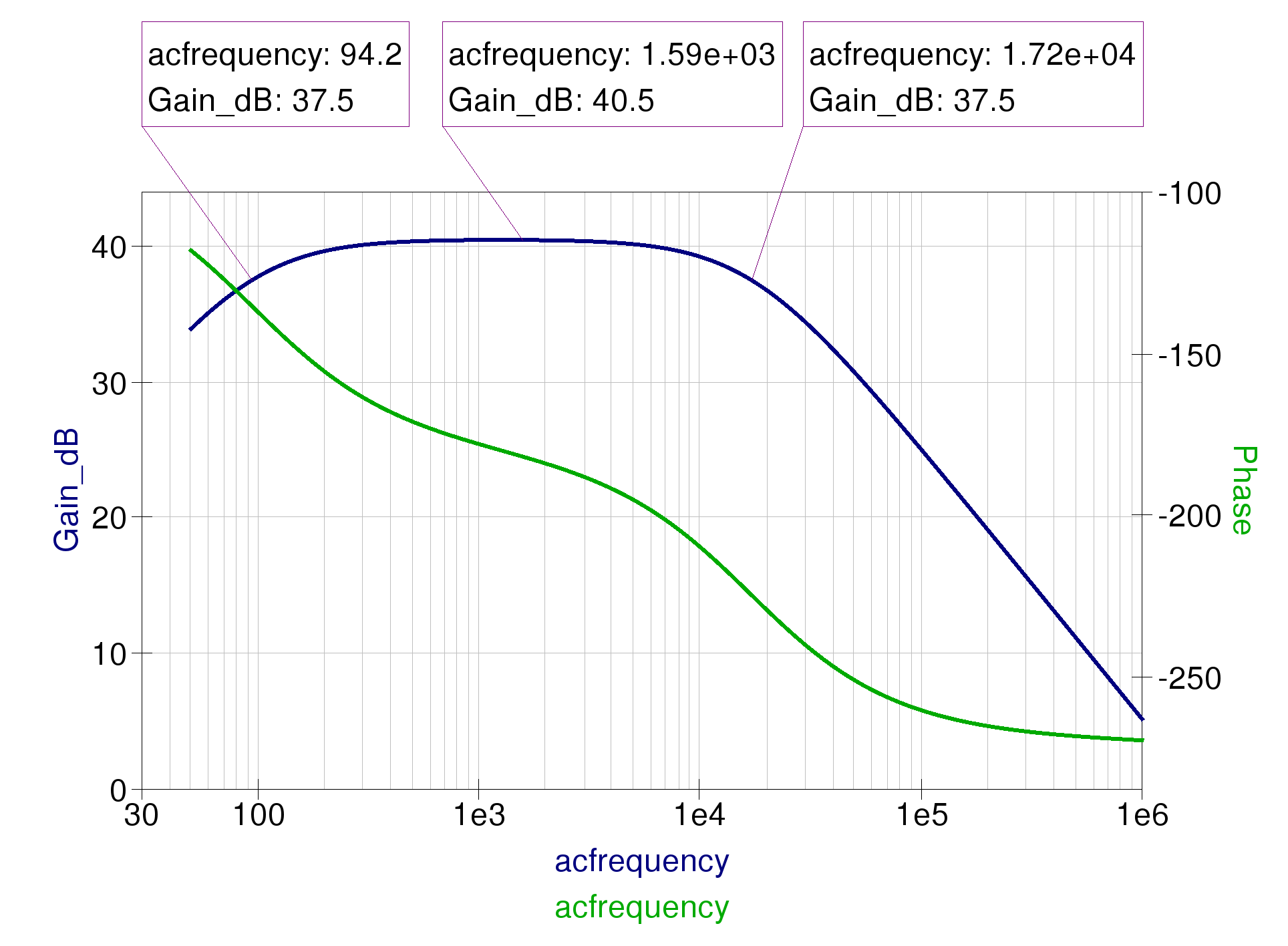

I ran the amplifier through simulation to confirm the filter design. The filtering isn't much to write home about but the gain is actually pretty good. I still have no idea of what the microphones will put out but I think this is a start, worst case ill have to do two stages and some more filtering. I plan on using ITEAD.cc so i have 50x50mm to work with...

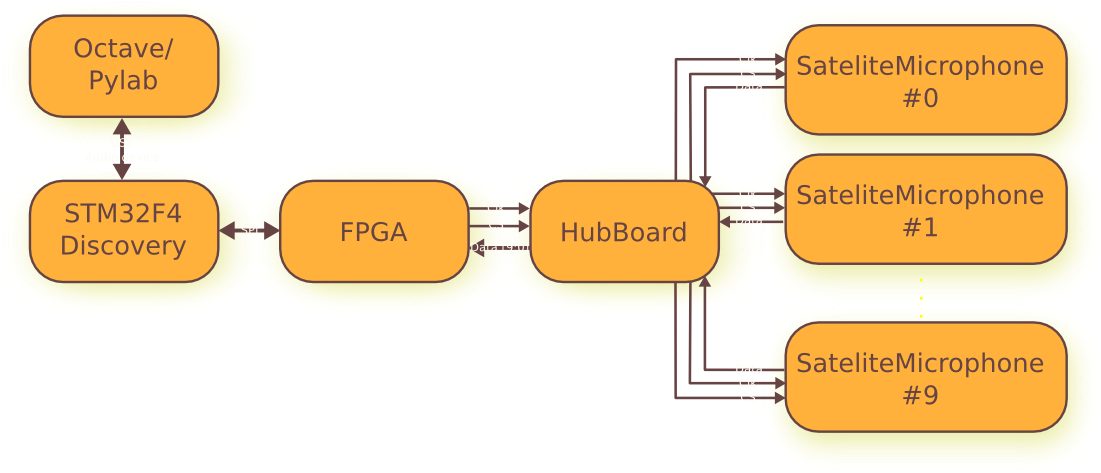

This far I have a pretty solid idea for how the system is going to work.

I want the final data to the computer to be a mono audio stream in one direction and commands going the other direction. I have a good STM32F4 library to do the USB interface with. To keep the FPGA design simple I'll implement an SPI slave with an optional IRQ line between the FPGA and the STM32F4.

The HubBoard will need to do level shifting, possibly impedance matching, and buffering of the CLK and CS lines.

I put up the project in a GitHub repo at: https://github.com/LeastSignificantBit/Phased-Array-Microphone-using-FPGA

Martin Berglund

Martin Berglund

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.