What is SpinalHDL ?

Spinal is a open source high-level hardware description language. It can be used as an alternative to VHDL or Verilog and has several advantages over those.

Also Spinal is not a HLS approch, its goal is not to push something abstract into flip-flop and gates, but by using simple elements (flip-flop, gates, if / case statments) create new abstraction level and help the designer to not rewrite always the same thing.

Note: Spinal is fully interoperable with standard VHDL/Verilog-based EDA tools (simulators and synthetizers) as the output generated by the toolchain could be VHDL or Verilog.

It also enables mixed designs where Spinal components inter-operate with VHDL or Verilog IPs.

Advantages of using SpinalHDL over VHDL / Verilog

As Spinal is based on a high-level language, it provides several advantages to improve your hardware coding:

- No more endless wiring - Create and connect complex buses like AXI in one single line.

- Evolving capabilities - Create your own buses definition and abstraction layer.

- Reduce code size - by a high factor, especially for wiring. This enables you to have a better overview of your code base, increase your productivity and create fewer headaches.

- Free and user friendly IDE - Thanks to scala world for auto-completion, error highlight, navigation shortcut and many others.

- Powerful and easy type conversions - Bidirectional translation between any data type and bits. Useful to load a complex data structure from a CPU interface.

- Loop detection - Tools check for you that there is no combinatorial loop / latch.

- Clock domains safety - The tools inform you that there is no user unintentional cross clock domain.

- Generic design - There are no restrictions to the genericity of your hardware description by using Scala constructs

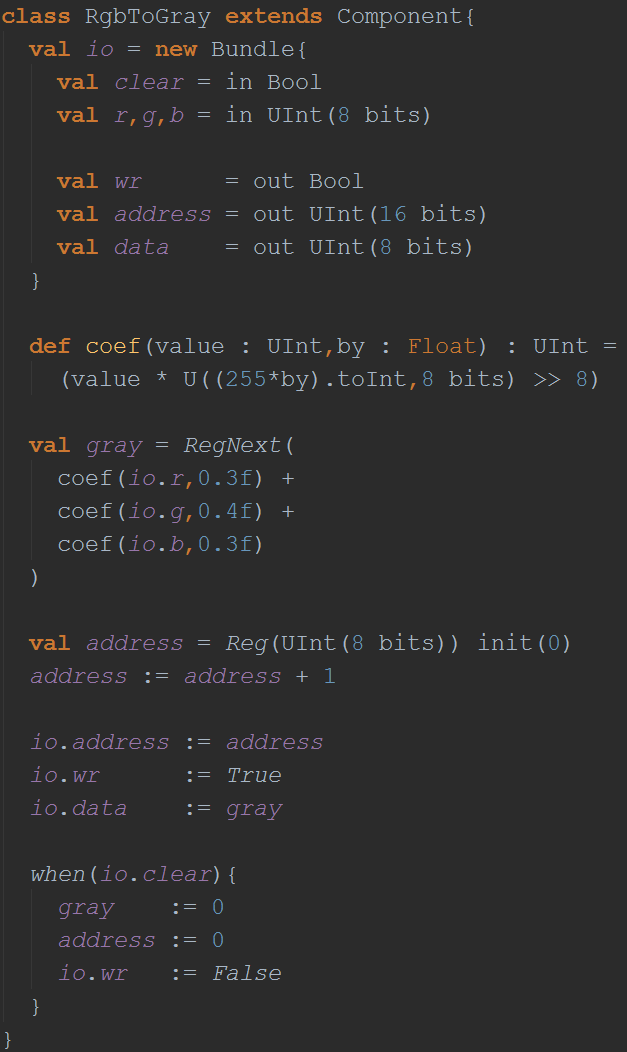

Example : RgbToGray

Let’s imagine a component which convert a RGB color into a gray one, and then write it into an external memory.

| io name | Direction | Description |

|---|---|---|

| clear | in | Clear all internal register |

| r,g,b | in | Color inputs |

| wr | out | Memory write |

| address | out | Memory address, incrementing each cycle |

| data | out | Memory data, gray level |

This example is a very simple one, SpinalHDL offer many more features. Do not hesitate to take a look into the online documentation or the online presentation.

Dolu1990

Dolu1990

Miguel Risco-Castillo

Miguel Risco-Castillo

Leonardo Suriano

Leonardo Suriano

Vicharak

Vicharak

ALXCO-Hardware

ALXCO-Hardware