Avalon bus-master peripheral driving bus-slaves (with HPS read-out and control)

-- External bus to Avalon Bridge

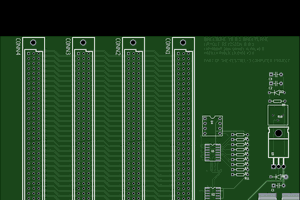

Student generated modules will need to be Avalon bus-slaves when

controlled by the HPS, but under some conditions will need to be

bus-masters. For instance, building a module which writes directly to

the VGA interface would require a bus-master ability. The first example

uses the University Progam External Bus to Avalon Bridge

(EBAB) module as a bus-master which addresses either the LEDs or the

HEX display to display numbers set on the toggle switches, and with a

write-enable using ~KEY[0]. The HPS C-code reads and displays the SW and KEY peripherials. The Qsys layout

has just the HPS, parallel ports for the LEDs, HEX display, switches,

and buttons, and the EBAB module. The LEDs and HEX display are hooked to

the

external-to-avalon

master. The SW and KEY are hooked to the HPS h2f_lw_axi_master. (top-level, hex decoder, project ZIP). This code ignores the Avalon ACK bit and does not read any data.

-- Controlling the bus-master from the HPS

In the second example, the HPS uses a keyboard command interface

to choose the HEX or LED device address which is used by the EBAB. The

FPGA side has a small state machine which counts time and uses the EBAB

to display the count on the HEX or LED devices. The state machine also

handles the bus-write setup and waits for the Avalon bus ACK. The Qsys layout

converts the switch PIO into an output getting data from the HPS

light-weight bus. This new output is used for the device address by the

EBAB. (top-level, project ZIP).

This example is a model of how a hardware computational unit might be

controlled by the HPS and interact with other bus-attached peripherials.

The bus transaction from EBAB to HEX display PIO takes two cycles

(write, ACK). I tested up to 100 MHz state machine rate, for a bus rate

of 50 million/sec.

--

The logical sequence is: A C-program outputs a bus address to the

h2f_lw_axi_master address (of the ARM) which is mapped to a PIO unit on

the Avalon bus. The PIO unit exports the address value to the FPGA

fabric, which also contains the EBAB. The EBAB uses the address (from

the PIO) to set its own write address back onto the Avalon bus.

-- Multiple bus-masters to one bus-slave

The Qsys bus generator constructs arbitration hardware for various

configurations of masters and slaves. I wanted to test the operation of

multiple bus-masters talking to one bus-slave. The previous example was

extended to have two EBAB units, one controlled as before with its bus

address controlled by a C program.

The other was set to always write to the HEX display. The phase of the

write-clock was set up so that they write at different times. Each

bus-master counts at different rates. The counts are displayed on the

HEX displays and for bus-master one, on the LEDs, when chosen. The Qsys layout shows that both the EBAB masters connect to the HEX display. (top-level, project ZIP).

--

A modification of the top-level module

changes the bus request rate to 3.1 MHz, uses the SW input to set the

delay between bus write-requests, and puts the two write-requests and

the two ACK bits on the GPIO_0 port for view on an oscilloscope. If the

separation is zero and addresses are set to the same bus_slave, then one write-request is stretched to two cycles (top trace) while the bus is busy with the other. If two different bus-slaves are addressed by the two bus-masters, or the time between write-requests is one cycle or more, then there is no collision and the write-requests are each one state-machine cycle

long. Synchronization in the bus-master state machines depends on

reading the ACK bits returned from the Avalon bus. Which write-request

actually gets stretched, when they are on the same cycle, seems to be

randomly determined by race-conditions.

-- Video display bus_master with HPS

A bus-master to control video display is useful for many projects.

Interfacing...

Bruce Land

Bruce Land

Ted Fried

Ted Fried

Keith

Keith

Samuel A. Falvo II

Samuel A. Falvo II

Seamus de Cleir

Seamus de Cleir

You could follow the link to the page

https://people.ece.cornell.edu/land/courses/ece5760/DE1_SOC/HPS_peripherials/index.html