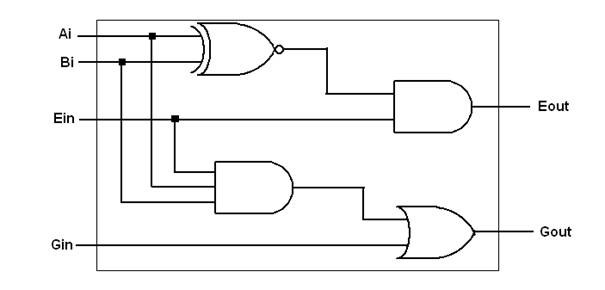

I was trying to test the ALU design presented previously when I realized something was wrong with the comparator. Now where did that design come from? I could not find it on the Internet (surprising) but this one looked good to me:

(source: http://fpgacenter.com/digit_dsgn/log_gates/comparator.php)

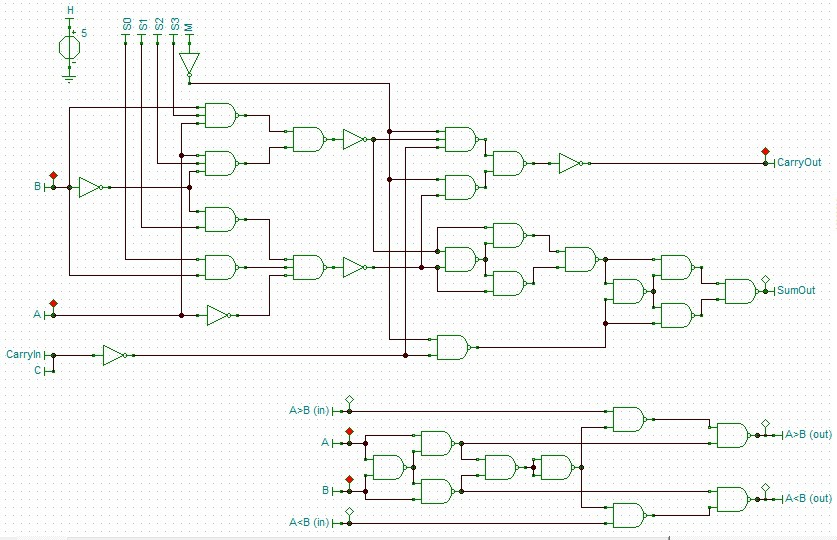

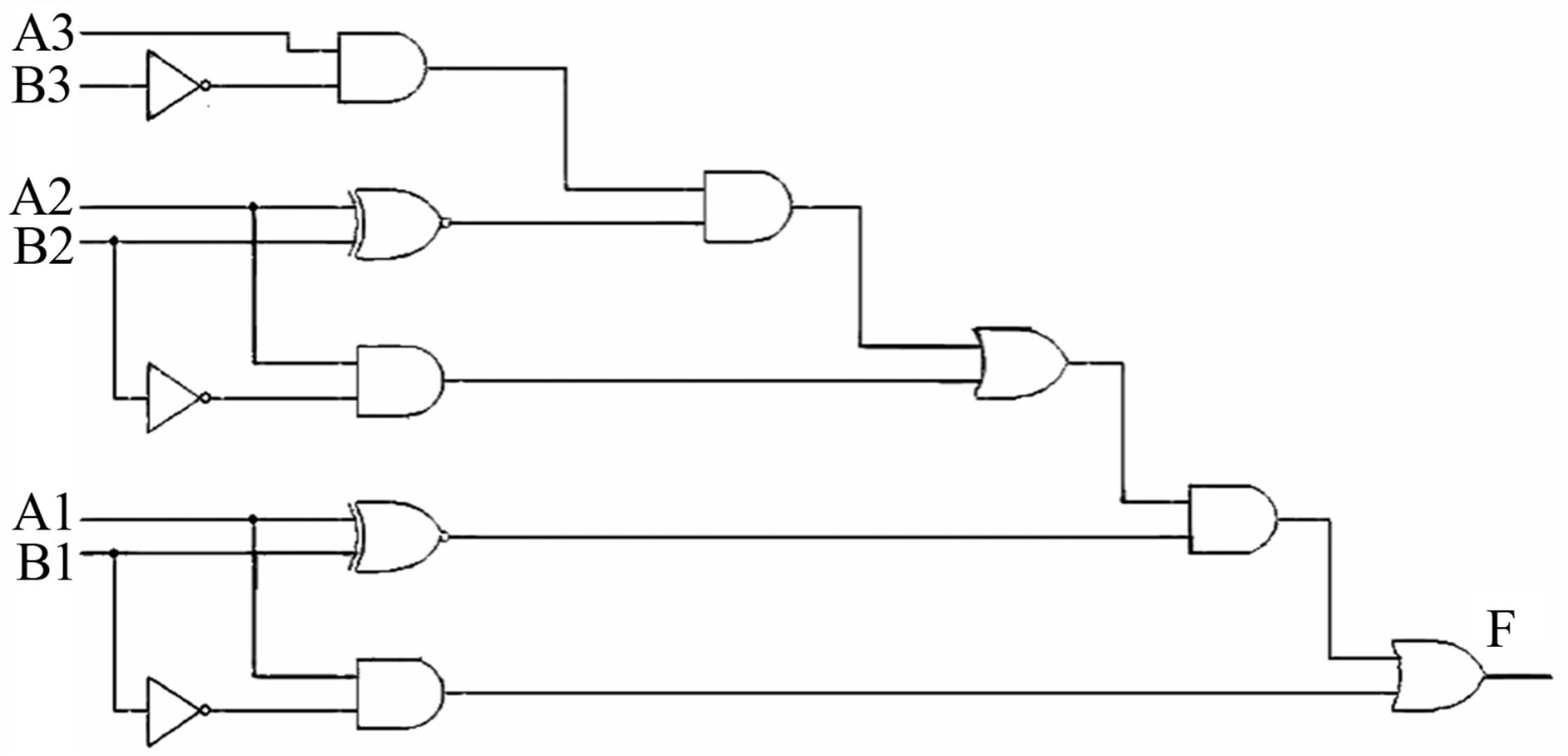

Anyway, not happy where did it come from? Eventually I found this:

(source: http://file.scirp.org/Html/2-7600304_41935.htm)

Which I recognised I had used as a base. This came from:

"Design of Low Power Comparator Using DG Gate" by Bahram Dehghan, Abdolreza Roozbeh and Jafar Zare.

This is a A>B comparator only.

So stripped out the bits I needed, converted to NAND gates and realized I could "mirror the circuit for A<B and reproduced my original circuit less the design error I had carried over. This time I did not to piggy-back off the ALU gates (so the comparator is now stand alone):

The Hazards of Teaching Yourself

In the above circuit I have some logic signal flags. Now I have had Tina Pro V5.5 for 10 years and did not know I could do this (the documentation is pretty bad). I have almost exclusively used Transient Analysis even for digital design. Now I am sure that if I did do a course then this feature would have been explained. (Note: I don't work in the electronics field. I was a mining engineer and we like to dig holes in the ground.)

Because Tina Pro 5.5 is pretty unstable I migrated to the Tina-TI version (and that does not have logic signal flags). I was only using Tina Pro 5.5 because I needed something better than Transient Analysis. If I went back then I would have to re-digitize most of my current work as Tina-TI does not export the really old file formats.

Crippled Software

I have looked at Tina 10 but the hobby versions are crippled for only small circuits and the unlimited version are crippling in price.

I have an old version of Cut2D (for CNC) that works really well and is unlimited. Cost about US$180 from memory a few years ago. The latest versions have gone the same way, crippled in capacity or crippling in price. Go figure! It not that there are no substitutes.

AlanX

agp.cooper

agp.cooper

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

This is nothing compared to a hardware mapped CPU!

AlanX

Are you sure? yes | no

Hi Yann,

The CPU design assumes that you use the JNC for handling Carry situations. The convention for the ALU is "+" equals "OR" so close but not quite. My version of "A" MINUS "B" would have been:

DEC "B"

OR/NOT "0"

PLUS "A"

JNC (if multi-byte)

My CPU sets the ALU B Operand to the previous ALU results.

The next trick was to hold the ALU status so that condition jumps can be make later.

In another version of the CPU, I use an unused NOP to set the Carry Flag at the cost of one chip.

Regards AlanX

Are you sure? yes | no

This sounds so convoluted ! :-D

Are you sure? yes | no

For the comparison, my approach is to compute the SUB instruction (A + (~B) + 1) and read the Carry output...

Are you sure? yes | no