Choosing the processor

I'm strongly in favour of the Z80.

A lot of people working with retro builds gravitate towards the CPU of their first computer. My first computer wasn't a Z80 machine - it was a TI-99/4A, based on the rather obscure TMS9900 processor - a reimplementation of an old TTL minicomputer processor in NMOS microprocessor format, an idea that really didn't work very well... the processor needed very fast RAM to make it work (because, like many minicomputer processors, it stored its registers in external RAM), but that made actually attaching a reasonable amount of RAM to the processor too expensive for a home computer. In order to be able to compete with computers using commodity DRAM, the TI-99/4A had to limit the memory attached to its processor to just 256 bytes: the rest of its 16KB of RAM was attached to the display processor and only indirectly accessible to the CPU. I'm not going to build a TMS9900 based machine.

My second computer was a Sinclair ZX Spectrum, and it was on the Spectrum that I first learned assembly programming (assembly programming for the TI required an expensive RAM expansion pack -- otherwise there wouldn't be any free RAM to load your program in -- and an external disk drive, neither of which I could afford). It was only later that I learned 6502 programming, and ever since I have held a sincere belief that the Z80 is a much more programmer-friendly processor.

In the 1981-1982 time period, the Z80 was available in 3 speed grades: the original 2.5MHz version, the Z80A (4MHz), and the Z80B (6MHz). The faster Z80H (8MHz) didn't show up until later, and in any case would have been expensive to use in 1982 as DRAM fast enough to keep up with it wasn't yet available, so more expensive static RAM would be necessary (or you could use WAIT states to reduce its memory access rate, but that slows it down far enough that you see almost no benefit for having the faster and much more expensive chip anyway). So the Z80B it is. Z80s are notoriously easy to overclock (Grant Searle asserts that every Z80A or B he has tested is able to manage at least 10MHz) so I have some flexibility to increase beyond 6MHz - I plan to do this in order to run at an integer divisor of my pixel clock (see video hardware below).

At 6MHz, a bus cycle lasts about 160ns -- it's exactly 160ns for 6.25MHz. In order to do this with no WAIT states (which would be ideal - WAIT states can really slow a machine down) I'll need to memory that responds within 240ns to each request (because the Z80 requires 1.5 cycle response time when fetching instruction data). This can be achieved with 4164-120 DRAM chips, which have a cycle time of 230ns, or a page mode cycle time of 120ns, plus 90ns RAS precharge + 20ns RAS-to-CAS delay when changing page. 4164-100 cost a bit more, but may help with implementing video hardware (see below); this has a page mode cycle time of 105ns, plus 95ns overhead on page changes.

(I originally planned to use 41256 chips to get a reasonably large memory capacity without making the board too big, but it seems those weren't available until 1983)

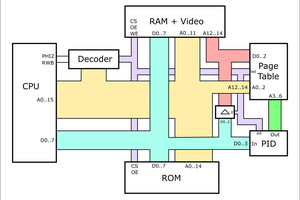

Memory design

How much of it should the system have, and how should it be organized?

Because of the speed constraints above, no commonly available 16Kb DRAM chip would be fast enough. And seriously, why bother? 64KB RAM is the minimum specification an 8 bit machine should ship with. Catering for smaller capacities will end up with a more expensive design so you can handle different installed amounts that within a couple of years nobody will ever want. The existence of the 16KB spectrum made the 48KB model harder to design, and more expensive, because they needed to share a board design.

It's tempting to just say 64KB and be done with it. It simplifies everything. But -- I want to design a machine that's superior to its competitors. And in very...

Read more »

Matt Stock

Matt Stock

Samuel A. Falvo II

Samuel A. Falvo II

Clyde Shaffer

Clyde Shaffer

Can you go into more detail about your HDMI video generation idea? Right now, I'm designing my FPGA logic to put out gun signals intended for an R-2R DAC network to drive an analog VGA. Although I've read the specs on DVI, I'm not up to speed on HDMI. I know HDMI is backward compatible with DVI 1.0, though, and what you're describing is a DVI video mode (baseline VGA was the lowest spec possible on DVI). However, I'm not putting my knowledge of DVI and your thoughts together; something seems missing. Is it possible to create a project log that goes into more details on this idea? Thanks!