An excellent explanation of Integrated-Injection Logic (I2L) is in the classic IEEE paper from R. A. Pedersen of Bell Labs. In the early 1970s, MOSFET logic had not evolved into the high-speed technology that NMOS in the mid-late 1970s and CMOS in the early 1980s would become. One promising development is that of I2L, which offered the speed of TTL with much lower power-use, as well as a very simple silicon topology that lent itself well to large-scale integration.

Given the excellent explanation of I2L in Pedersen's paper, I won't attempt to explain I2L operation here.

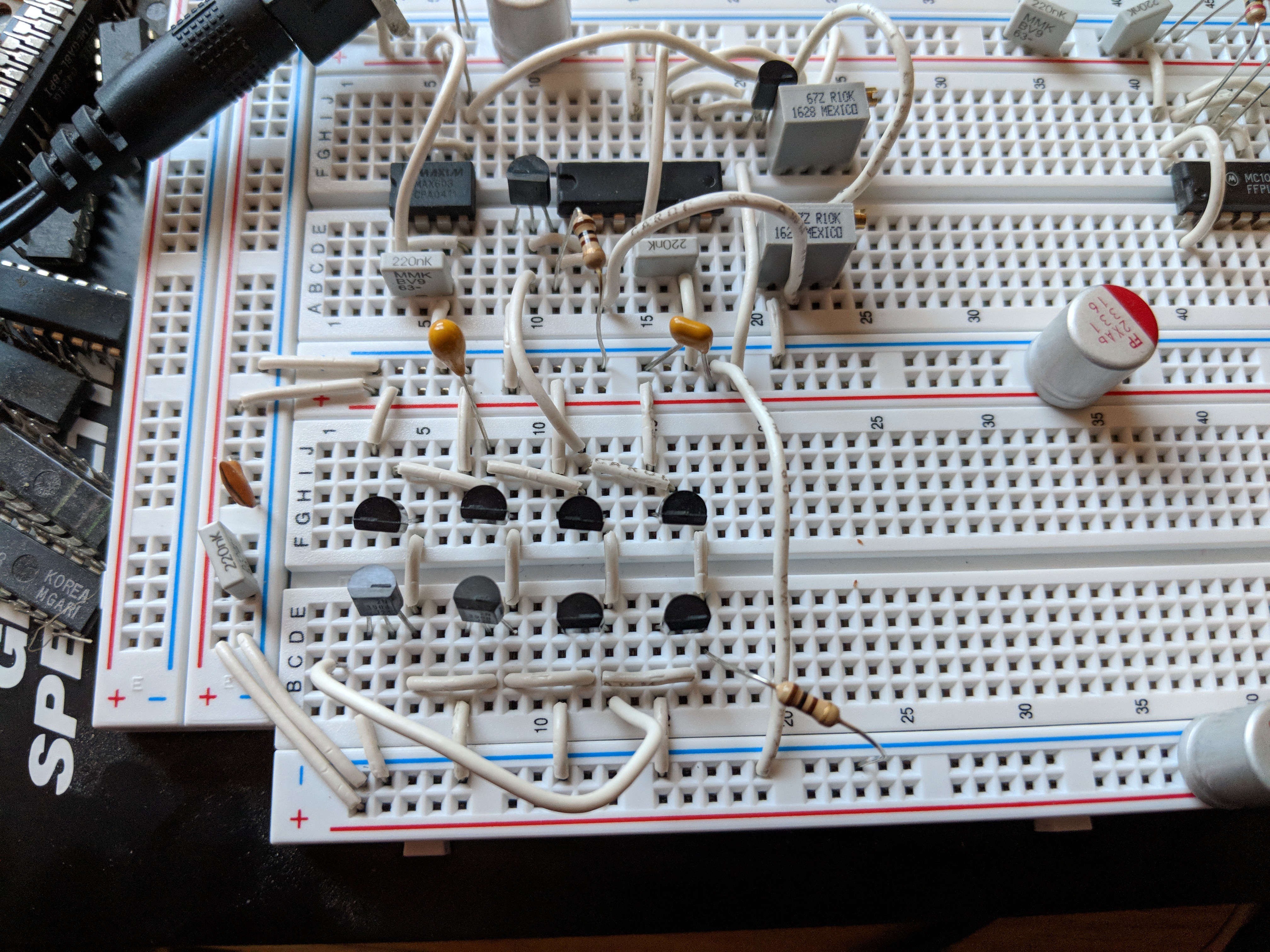

Instead, here's the LTspice circuit of a simple 3-inverter I2L ring oscillator.

Simulation with ON Semi models suggest operation frequency around 38MHz; subsequent simulation adding 5pF to each collector-node suggested a realistic proto-board frequency around 32.3MHz.

Circuitry to the upper-left is a 1V power-supply regulator and a bias-voltage generator for the PNP current-injectors. Adjusted for 2.6mA injection, the circuit operates around 30.9MHz - remarkably close to the simulation value! This is roughly 5.4nS propagation delay per inverter, with a speed-power product of 14pJ (this is considerably higher than ~1pJ of actual monolithic I2L where the transistors are optimized, but quite a bit better than 100pJ of standard TTL in the early 1970s).

Monolithic I2L merges the PNP current-sources with the NPN switches, making it compact.

It occurs to me to look for low-voltage, low-power transistors that more closely match the characteristics of the monolithic transistors used in classic I2L to see if I can get the speed-power product down to 'classic' levels.

Electroniclovers123

Electroniclovers123

Yann Guidon / YGDES

Yann Guidon / YGDES

kamalkedin123

kamalkedin123

engineerkid1

engineerkid1

I recall the acronym from college days (that was late 80s), but faced it in practice just recently. It's a behemoth Toshiba Dolby B/C/EQ processor with I2L serially-controlled digital front end. The latter is powered with an external resistor that sets logic supply current at predetermined value. The datasheet warned that this arrangement is tricky: +/-10% tolerance in current, or may go kaboom at high or low temperature extremes. It appears to be quite safe at home temperatures, but certainly not good for outdoor temps. Remember how finicky early CMOS chips were? well, this one is just as tricky, but it comes from around 1990!

So, in the end it's good that I2L finally gave way to CMOS - once the CMOS teams learnt how to integrate quality analogue circuitry.