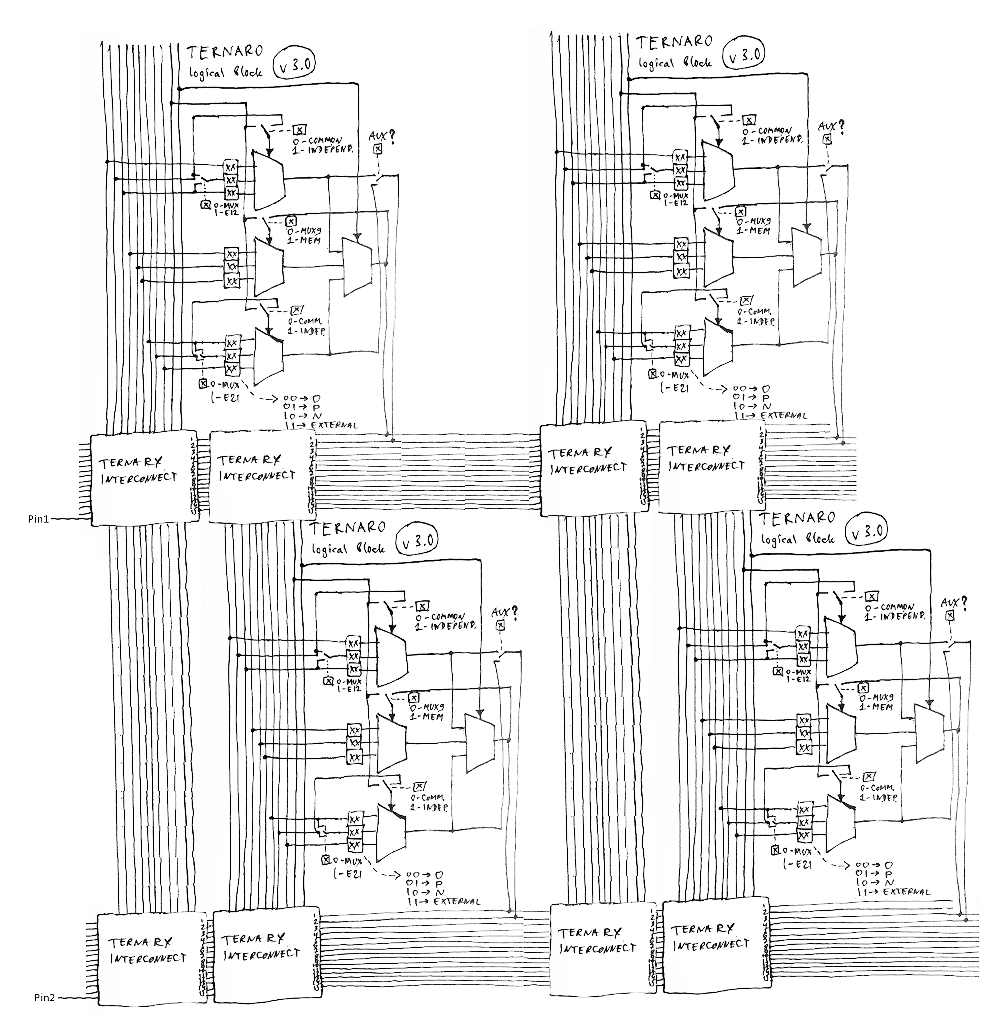

As I wrote before it should be a grid of 7 x 9 logic blocks (63 total) where every horizontal "channel" is having 15 lines and one of which is a pin (so it is 9 pins total), but less number of channels is also possible - for example below is 2 x 2 (unpractical because of only 2 IO pins are there, but good enough for demonstration purposes):

So in case of full scale 9 channels (one horizontal channel per every IO pin) every TERNARO logic block will need NINE interconnect blocks to cross every channel, so total length of bitstream will be (4+9*6)*63 = 3654 bytes (from up to down from left to right) and this bitstream needs to be pushed into the chip by external microcontroller (binary one of course).

About testability - test address inputs TA0...TA6 (address is binary) will choose which HORIZONTAL ternary line needs to be connected to test output TEST - it is 15*9=135 of them, but as we can see every 15th one is an IO pin, so we obviously have direct access to pins already and we can skip all of them so it's 135-9=126 total plus 1 output for SDO - serial data out for Slave SPI - if TA=0:

0000000 (0) - SDO output of Slave SPI

0000001 (1) - signal 1 of 1st channel

0000010 (2) - signal 2 of 1st channel

0000011 (3) - signal 3 of 1st channel

0000100 (4) - signal 4 of 1st channel

0000101 (5) - signal 5 of 1st channel

0000110 (6) - signal 6 of 1st channel

0000111 (7) - signal 7 of 1st channel

0001000 (8) - signal 8 of 1st channel

0001001 (9) - signal 9 of 1st channel

0001010 (10) - signal 10 of 1st channel

0001011 (11) - signal 11 of 1st channel

0001100 (12) - signal 12 of 1st channel

0001101 (13) - signal 13 of 1st channel

0001110 (14) - signal 14 of 1st channel

0001111 (15) - signal 1 of 2nd channel

0010000 (16) - signal 2 of 2nd channel

.....

1111110 (126) - signal 14 of 9th channel

1111111 (127) - Vref (for testing purposes)And we have 1 extra signal (when TA=127) that could be used for example to test internal Vref level...

SHAOS

SHAOS

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.