Now it's currently developed as simulation of electronics systems with any-bit and any-trit numbers using modern C++ (2011 and above).

Later TRCM also could have:

- converter from Verilog to C++ for faster simulation/verification with C++ "testbench";

- converter from C++ representation to VHDL to synthesize it for your favorite FPGA/CPLD;

- converter from Logisim to C++ for fun etc.

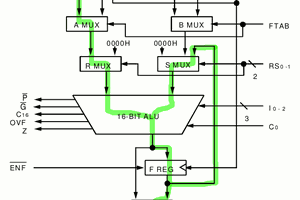

Main idea was to stop using dedicated wires for inputs or outputs in high-level simulation - wires are just wires - each of them could be input or could be output or could be disconnected during simulation. So TRCM (full name is TRCMath C++ library) defines 10 states of the wire to cover all possible scenarios for binary and ternary digital electronics (revised on August 18th 2018):

// Wire states:

const char TRUE = 'P'; /* connected to positive voltage */

const char MAYBE = 'O'; /* connected to intermediate voltage */

const char FALSE = 'N'; /* connected to the ground */

const char ANYBIT = 'X'; /* for comparisons only */

const char ANYTRIT = 'Y'; /* for comparisons only */

const char NC = 'Z'; /* not connected (high impedance) */

const char PULLUP = '1'; /* weak pull-up to positive voltage */

const char PULLDOWN = '0'; /* weak pull-down to the ground */

const char PULLMID = '-'; /* weak pull-middle to intermediate voltage */

const char INVALID = '?'; /* conflict on the wire (simulation halts) */

// Aliases:

const char HIGHIMP = NC;

const char POSITIVE = TRUE;

const char NEUTRAL = MAYBE;

const char NEGATIVE = FALSE;

Also TRCM gives user ability to use N-bit or N-trit numbers and perform math with them. Currently available classes:

Signal - the same as Wire<1>;

Wire<N> - N wires;

Uint<N> - N-bit unsigned integer;

Sint<N> - N-bit signed integer;

Tint<N> - N-trit balanced ternary integer (sign is already embedded into this representation naturally).

A few existing TRCM classes support simulation: System, Entity, Connection and RuntimeException.

Source code is available on GitLab under GPL v3: https://gitlab.com/ternary/trcm

And I will post examples of TRCM usage here in this projects as logs...

SHAOS

SHAOS

M. Bindhammer

M. Bindhammer

daovanhoa12

daovanhoa12

Yann Guidon / YGDES

Yann Guidon / YGDES