When I was coming up with new Register Transfer Scheme, and in general while rethinking the design approach for this CPU, I realised that the explicit state machine will be the way to go. At the time I thought it would consist of quite a few of states. But while devising the ways words need to be shuffled around the CPU (to enumerate needed states) for every instruction, I found out that there is a lot of commonalities between some of the states, and they can be grouped so that difference between them would be one or two signal lines. It occurred to me that there is a way to make the number of states low, but have the variations inside states that would be disambiguated via combinatorial circuits. Example would be Load/Store state, they have a common pattern for addressing logic, but different for the data moving logic. Yet, this difference can be wholly controlled by just one bit in instruction, which makes trivial the disambiguation.

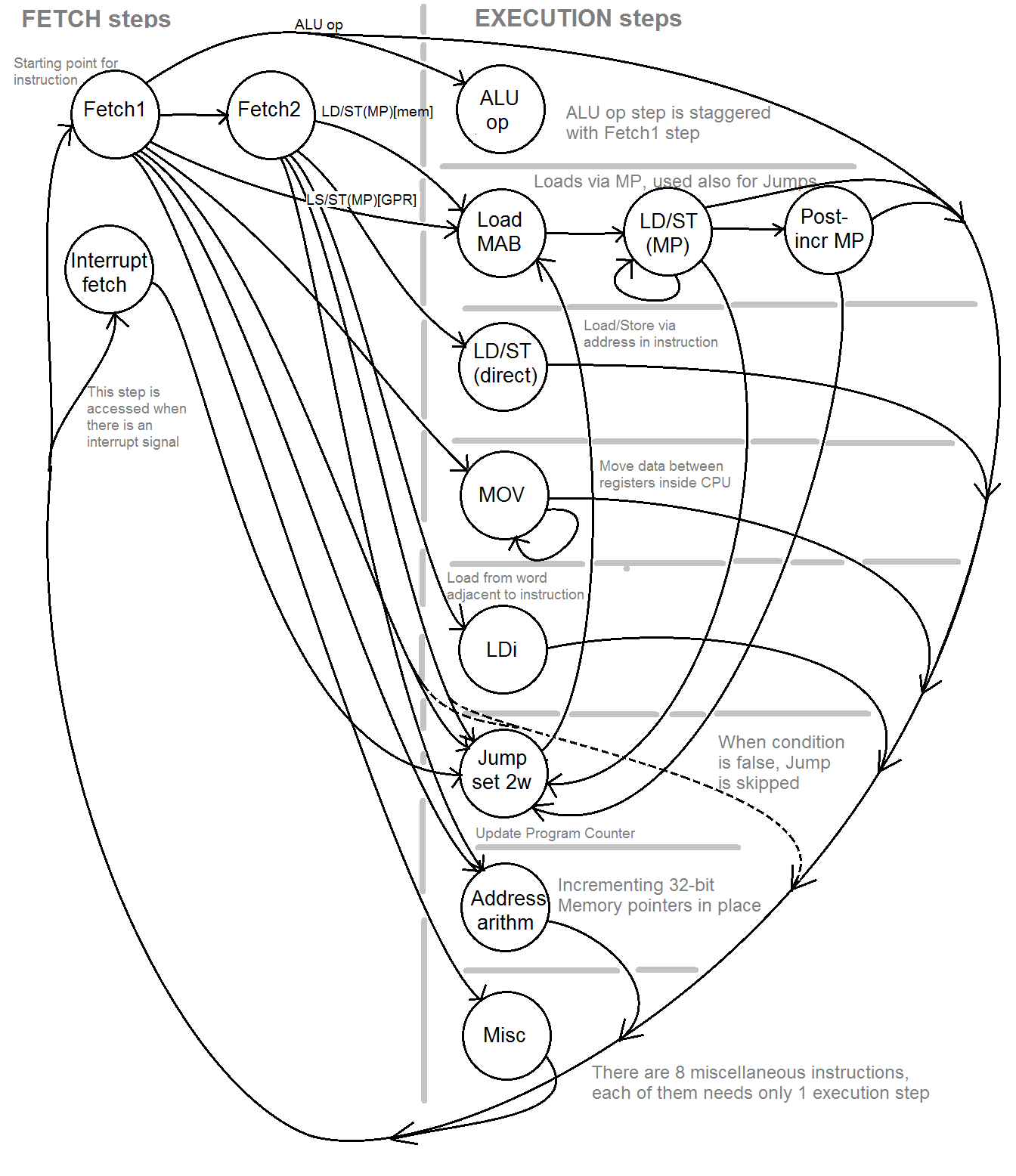

Thus I weeded the total number of states to 3 fetch states and 10 execution states.

Here is a diagram which shows these states and transitions between them:

As can be visible from the diagram, there are 8 instruction types:

1: ALU operations -- all are executed in 1 step and decoded inside Calculating Core; the next instruction is fetched in parallel

2: Loads/Stores via MP +offset -- set of 8 instruction pairs (load/Store) of variable length of execution

3: Loads/Stores via direct address

4: MOV -- copying of data between registers

5: LDi -- loading immediate value into register

6: Jumps -- set of 8 conditional and 2 unconditional instructions updating Program Counter, use the same states as (2)

7: Address Arithmetic -- arithmetic operations on 32-bit values in MP (adding 8- and 16-bit signed values to MP)

8: miscellaneous -- different instructions like NOP, HLT, SetIM, multi-word prefix etc.

These instructions comprise the full set intended for my CPU.

Pavel

Pavel

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.