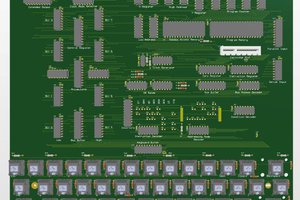

TD4 by itself is very primitive architecture - it can't even add it's registers together! There is only 16 bytes for program code and no RAM. Of course, it's easy to understand, but for something serious (think OS) that's absolutely not enough!

So, the plan:

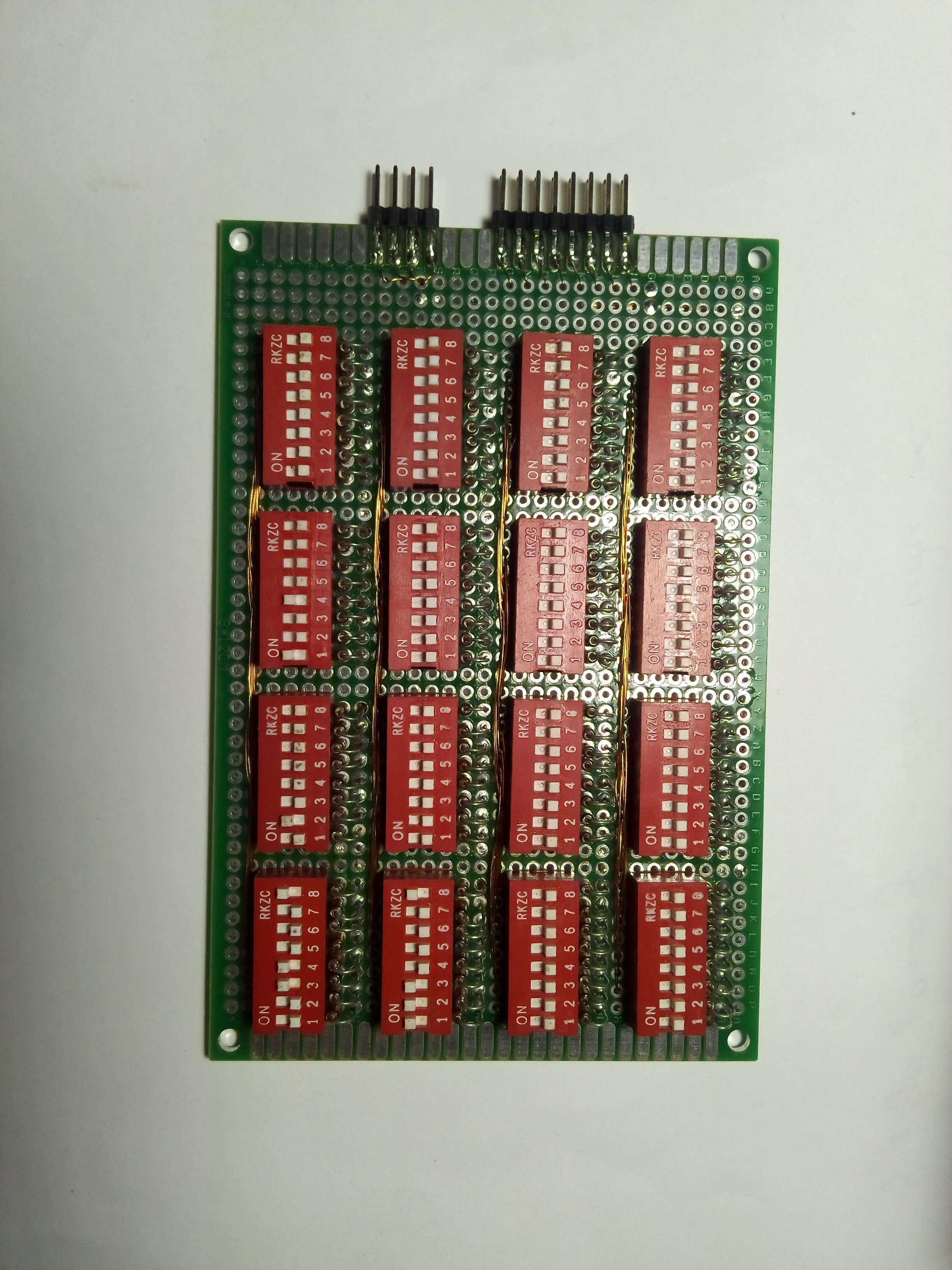

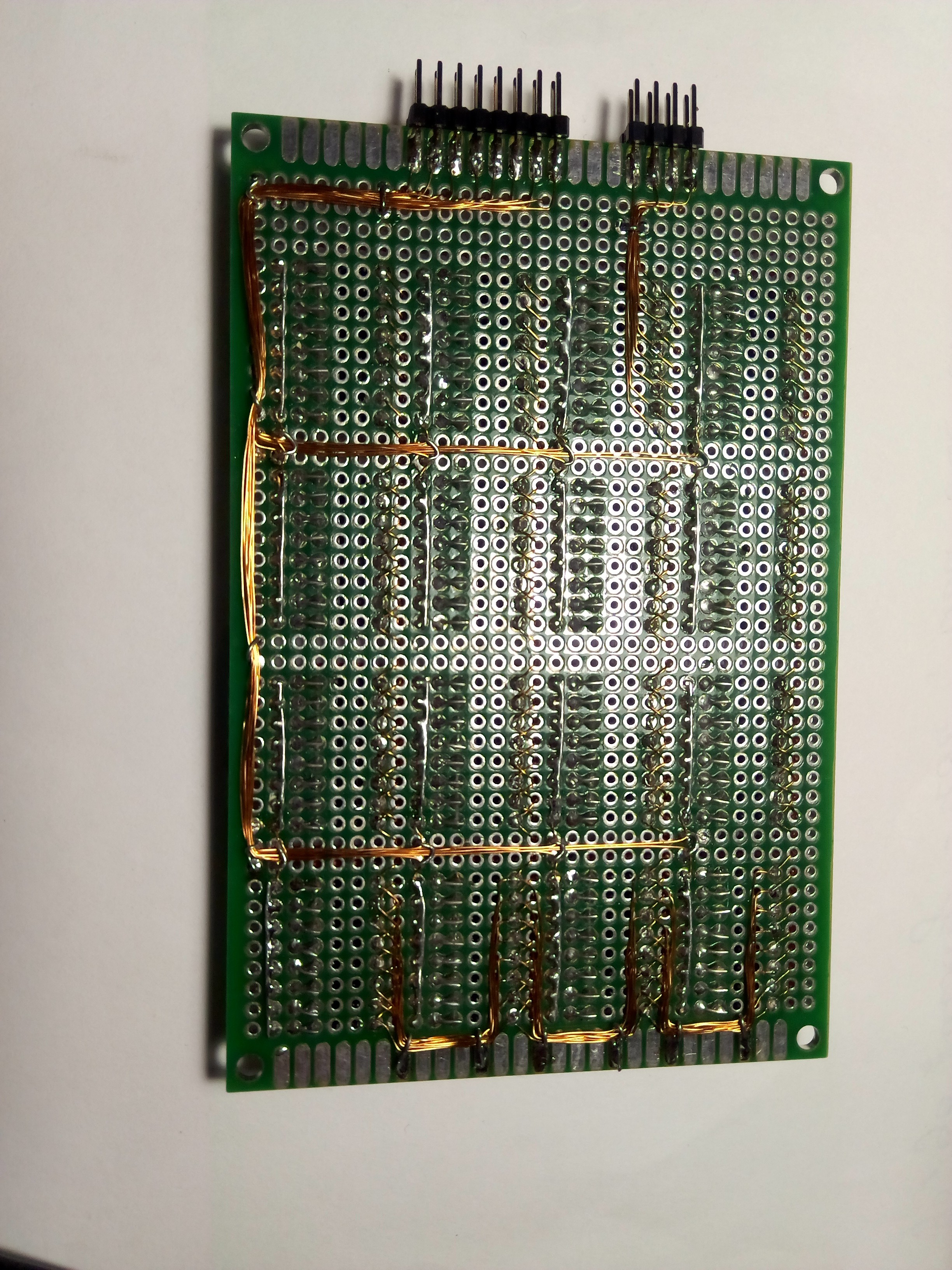

- Add RAM

- Add switchable ROM banks

- ...

- Software!

But, there are a few tricky moments.

First and foremost - I want to maintain backward compatibility with existing programs for TD4. It's not very hard, but gives a restriction to work with:

- I can't change existing opcodes (there are 12 out of 16 now)

This means I can only use 4 additional instructions to implement all the features I want.

Currently, those 4 instruction are distributed like this:

- LD Imm - load from RAM to register B

- ST Imm - store to RAM from register B

- SWM Imm - switch RAM (memory) bank

- SWI Imm - switch ROM (instruction) bank

RISCy, isn't it?

Also, there is an age-old workaround - it's possible to hook up additional hardware to the I/O bus and control it using IN and OUT instructions. I consider this as a way to add some interedting functionality, like external ALU or even UART (communications!).

Another moment is jumps between ROM banks. I'm still not sure about the implementation details, so I skip this for a while.

Vladislav Mlejnecký

Vladislav Mlejnecký

ErwinM

ErwinM

This looks like a very good implementation.

We have a project called TPS Myco - a 4 bit processor system with all of the bells and whistles, but in software ...

and it might fit to expand this processor in the same direction.

We have 256 addresses using a 4 bit page register in addition to the program counter.

MyCo now runs on nano, microbit, RPI PICO and others,

but I always wanted an even limited version in chips..

And your approach looks quite close. 4 instructions could be implemented without decoding:

1n output nibble to output

2n delay execution by 16 different values

3n is JUMP Back in MyCo, but could be a JUMP

xn to be defined.

There is a downoloadable simulator - adaptable to the different implementations.

There is even an online version of TPS/MyCo with assembler at

https://wkla.no-ip.biz/ArduinoWiki/doku.php?id=en:arduino:arduinosps:tpsass:mnemonics

and there are 3 books about it on amazon already.

One of them describes it and you can just use pen and paper

- no hardware required to "run" the 40 examples. All fully described in the book

https://www.amazon.co.uk/Workbook-Executing-Processor-Execute-Hardware/dp/B08MN15NMQ/ref=sr_1_25?qid=1690218282&refinements=p_27%3AJuergen+Pintaske&s=books&sr=1-25

The other 2 books are here and show the different hardware implementations

https://www.amazon.co.uk/Learning-Programming-MyCo-Juergen-Pintaske/dp/B095GCZQY9/ref=sr_1_24?qid=1690218282&refinements=p_27%3AJuergen+Pintaske&s=books&sr=1-24

https://www.amazon.co.uk/Programming-Myco-TPS-simulate-independent/dp/1731232535/ref=sr_1_31?qid=1690218282&refinements=p_27%3AJuergen+Pintaske&s=books&sr=1-31

I am looking forward to more of your design.