Full project for iCEcube2 software configured for iCE40UP5K-SG48 FPGA device:

https://cdn.hackaday.io/files/1623976947993248/iCEcube2-retro1t.tar.xz

It's Retro-V v1.0.0 soft core with "Hello RISC-V!" test program ( provided by @Frank Buss ) that is stored as ROM:

/*

Frank Buss: compile like this: riscv32-unknown-elf-gcc -O3 -nostdlib test1.c -o test1

or

riscv64-unknown-elf-gcc -march=rv32i -mabi=ilp32 -O3 -nostdlib test1.c -o test1

*/

void _start()

{

volatile char* tx = (volatile char*) 0x40002000;

const char* hello = "Hello RISC-V!\n";

while (*hello) {

*tx = *hello;

hello++;

}

}

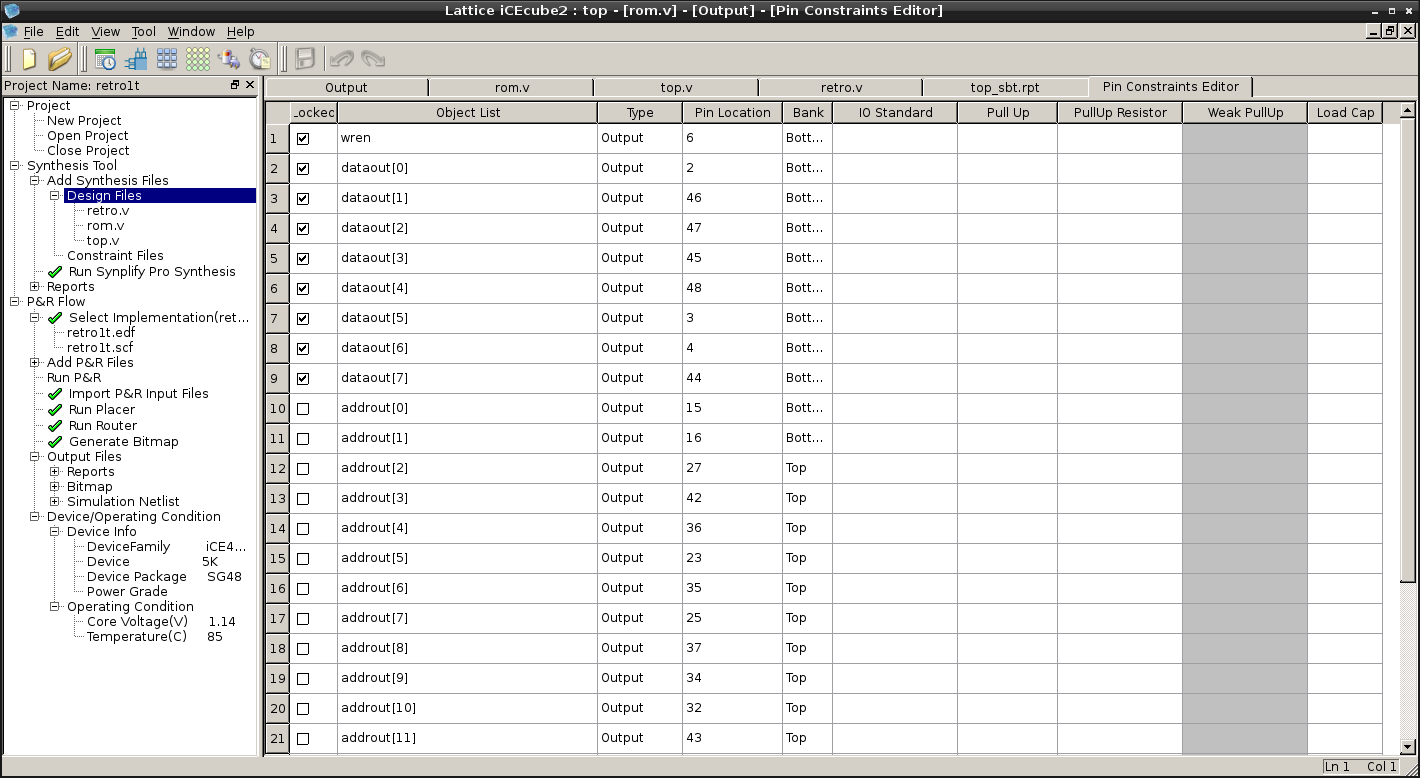

I locked data output 8-bit bus to bottom-left pins of UPduino:

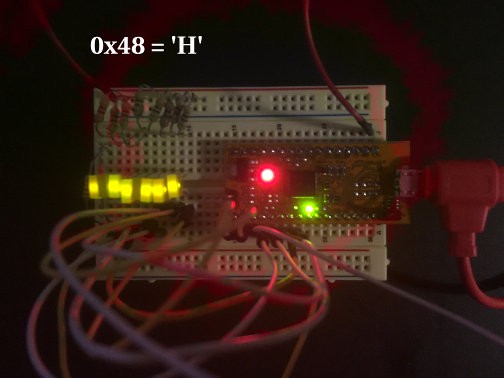

8 LEDs connected to them will "print" message character by character (LEDs show inverted bits):

So it prints:

01001000 = 0x48 = 'H'

01100101 = 0x65 = 'e'

01101100 = 0x6C = 'l'

01101100 = 0x6C = 'l'

01101111 = 0x6F = 'o'

00100000 = 0x20 = ' '

01010010 = 0x52 = 'R'

01001001 = 0x49 = 'I'

01010011 = 0x53 = 'S'

01000011 = 0x43 = 'C'

00101101 = 0x2D = '-'

01010110 = 0x56 = 'V'

00100001 = 0x21 = '!'

00001010 = 0x0A = '\n'

Source code is also uploaded to GitLab:

https://gitlab.com/shaos/retro-v/tree/master/FPGA/iCEcube2-test1

As you can see CPU clocked by 24th bit of the counter driven by high-speed oscillator, so it's like 16 millions times slower - in order to visually see what is going on there - blue blink is clock, red blink is write out (a character on 8 LEDs).

Design statistics:

------------------

FFs: 336

LUTs: 2211

RAMs: 4

IOBs: 25

GBs: 5

PLLs: 0

Warm Boots: 0

SPIs: 0

I2Cs: 0

HFOSCs: 1

LFOSCs: 0

RGBA_DRVs: 1

LEDDA_IPs: 0

DSPs: 0

SPRAMs: 0

FILTER_50NSs: 0

Logic Resource Utilization:

---------------------------

Total Logic Cells: 2313/5280

Combinational Logic Cells: 1977 out of 5280 37.4432%

Sequential Logic Cells: 336 out of 5280 6.36364%

Logic Tiles: 342 out of 660 51.8182%

Registers:

Logic Registers: 336 out of 5280 6.36364%

IO Registers: 0 out of 480 0

Block RAMs: 4 out of 30 13.3333%

Warm Boots: 0 out of 1 0%

SPIs: 0 out of 2 0%

I2Cs: 0 out of 2 0%

HFOSCs: 1 out of 1 100%

LFOSCs: 0 out of 1 0%

RGBA_DRVs: 1 out of 1 100%

LEDDA_IPs: 0 out of 1 0%

DSPs: 0 out of 8 0%

SPRAMs: 0 out of 4 0%

FILTER_50NSs: 0 out of 2 0%

Pins:

Input Pins: 0 out of 39 0%

Output Pins: 25 out of 39 64.1026%

InOut Pins: 0 out of 39 0%

Global Buffers: 5 out of 8 62.5%

PLLs: 0 out of 1 0%

IO Bank Utilization:

--------------------

Bank 3: 0 out of 0 0%

Bank 1: 0 out of 0 0%

Bank 0: 13 out of 17 76.4706%

Bank 2: 12 out of 22 54.5455%

SHAOS

SHAOS

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.