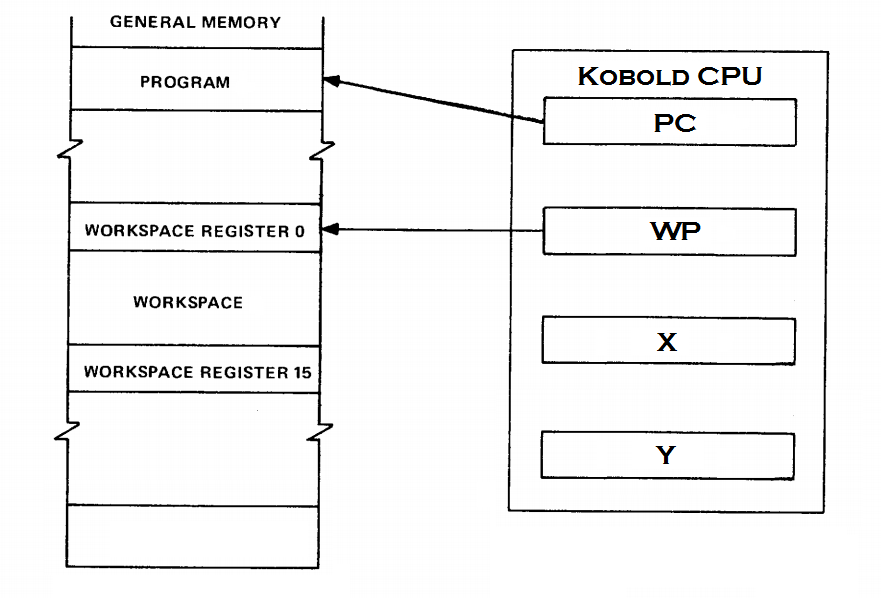

For the instructions, there will be the following registers visible:

Hardware address registers: (20 bit wide)

PC program counter

WP workspace pointer

X index register

Y index register

Registers in RAM (16 bit wide): R0 - R15

The WP register points to the location of R0.

The instructions will follow the assembly format of the PDP11 computer.

Most instructions will have two operands, like:

MOVB #17,R4 ; load register R4 with the value 17 (decimal)

Instructions handle a single byte or a word (2 bytes).

Possible instructions are:

MOVB src,dst ; move data (byte size) ADDB src,dst ; add data (byte size) SUBB src,dst ; subtract data (byte size) BISB src,dst ; bit set (byte size) BICB src,dst ; bit clear (byte size) BITB src,dst ; bit test (byte size) CMPB src,dst ; compare (byte size) MOV src,dst ; move data (word size) ADD src,dst ; add data (word size) SUB src,dst ; subtract data (word size) BIS src,dst ; bit set (word size) BIC src,dst ; bit clear (word size) BIT src,dst ; bit test (word size) CMP src,dst ; compare (word size) BR label ; branch. conditional versions also available JSR label ; jump to subroutine RTS ; return from subroutine

There will be more instructions, but these are the main ones.

Now the addressing modes:

Rn ; general register X, Y, WP ; address register (Rn) ; register indirect (Rn+) ; register indirect with post-increment disp(X) ; indirect with displacement, displacement 0-15 words disp(Y) ; indirect with displacement, displacement 0-15 words #number ; immediate data label ; zero-page memory location

Most instructions will be 2 bytes (16 bits).

There will be special instructions to load the four upper bits of X, Y and WP. This might be done with instructions that handle LONG operands (4 bytes).

Due to the limited number of opcodes available, not all combinations of addressing modes will be available in the final instruction set.

It is under investigation to make the instruction encoding equal to the encoding of the PDP11.

Well all that has to be done is write microcode to implement this.... Oh wait, there is no hardware yet....

[edit: new instructuction set is here]

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.