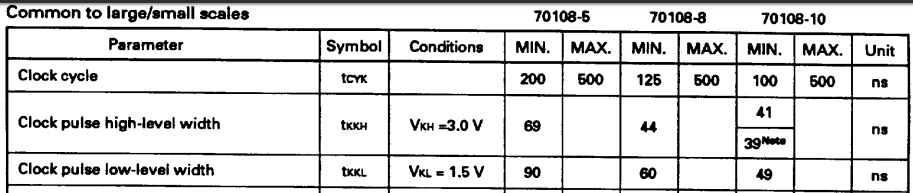

As the title said. Here we are trying to write up a simple oscillator for the V20. It looks like the V20 allows a square wave with 50% duty cycle, as long as you exceed these minimum values:

(NEC V20 Datasheet)

Here is a simple Verilog code for the oscillator:

module oscillatorV20(input clk, output reg clkV20);

reg [31:0] counter = 0;

always @(posedge clk) begin

if (counter == 8'd5) begin

counter <= 0;

clkV20 <= !clkV20;

end

else begin

counter <= counter + 1;

end

end

endmodule

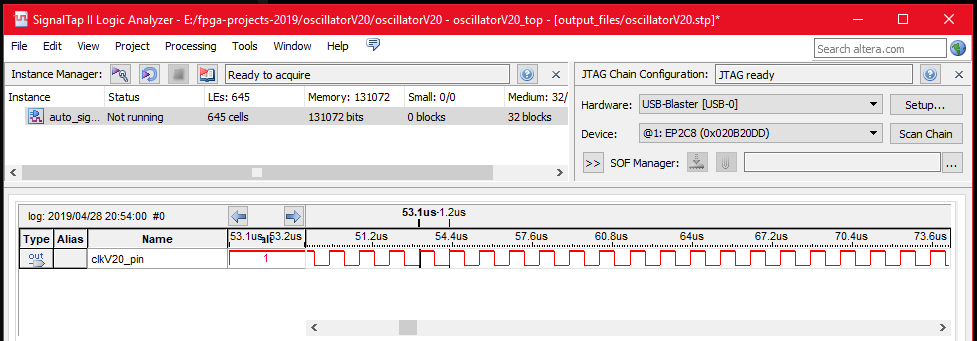

And using SignalTap 2, we see this as an output (this is an example 1 MHz square wave, and I'll tune to the 2 MHz after this):

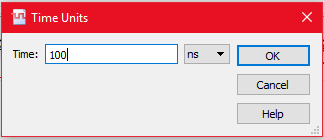

The problem with the little time bar was, I have to manually key in the "Time Units" (right click on the time bar, and click "Time Units"). Enter 100ns inside:

As this is working, my next step will be wiring the thing up to the FPGA board (ASK2CB) and check whether the ALE pin are pulsing or not.

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.