(see above for lexical information)

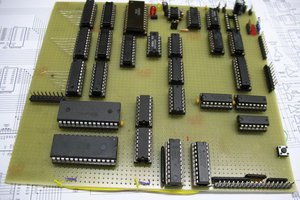

Trinium CPU

General

- data bus 9 trits (1 Tryte)

- addr bus 27 trits (3 trytes)

the CPU instructions will be based on the 8080 assembly, some instruction for the ternary side will be added

Register

On the Trinium Architecture there will be 5 GPR, the 4 usual in binary cpu plus 1 extra

- a : accumulator

- b : base

- c : counter

- d : data

- e : extra register

Each register is a "triplet" of tryte, a Word. Register can be accessed by Word or by Tryte in high, mid or low possition :

for exemple register `a` :

- ax will get the whole word

- ah will get the hight tryte

- am will get the middle tryte

- al will get the lower tryte

Lexical Informations :

- 1 Tryte = 9 Trits

- 1 Word = 3 Trytes = 27 trits

- 1 TWord = 27 Tryte = 729 trits

- GPR : Generale Purpose Register

- SP : stack pointer

- IP : Instructions Pointer

T4lus

T4lus

ammarbhayat28

ammarbhayat28

jaromir.sukuba

jaromir.sukuba

Szoftveres

Szoftveres

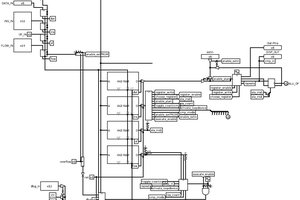

It is not that hard, the interface face glue is not necessary, as you have + and 0 as part of the Trinary logic, so you design your Trinary gates as either input 0+ or output 0+. There are 19683 two input/output gates to choose from, many have this form. So Trinary is 100% compatible with binary, though binary does not have a "-" you can use a selected Unary gate to convert. There are 27 Unary gates ( one in one out) that can be used to convert any logic, where binary has only 2 (buffer, inverter).