60MHz Bandwidth 250Msps Probe-Scope

The Probe-Scope is an open source 60MHz 250Msps oscilloscope probe with all guts built right in, that plugs directly into your PC via USB

The Probe-Scope is an open source 60MHz 250Msps oscilloscope probe with all guts built right in, that plugs directly into your PC via USB

To make the experience fit your profile, pick a username and tell us what interests you.

We found and based on your interests.

We'd like to thank our two sponsors for this project:

PCBWay, who was the manufacturer for all our PCBs and who also did the assembly for the final boards, kindly offered us a substantial discount on our final PCBAs. They have consistently made high quality PCB(A)s and have been responsive and pleasant to work with, and their low prices have helped us keep costs down on the job and made many personal projects (like this) affordable that wouldn't have been otherwise.

Marcus Engineering, LLC, the mutual employer of all our team members, paid for our final round of boards, which we're very grateful for since these were quite expensive in prototype quantity. At Marcus Engineering we provide high-end electronics engineering and product development services covering the entire product development lifecycle; we are based in Tucson, AZ.

We know you have a lot of projects to get through, so we’ve put together this brief on our project as it pertains to the criteria of the Hackaday Prize.

First of all, what is the Probe-Scope? It’s an open-source oscilloscope running at 250Msps with 60MHz of bandwidth, in the form factor of a cable; imagine you cut the BNC end off of an oscilloscope probe, and replaced it with a USB port: that’s the Probe-Scope.

The Probe-Scope is an innovation in the world of oscilloscopes, bridging the gap between the current low cost, low performance open-source oscilloscopes, and professional, expensive, closed-source oscilloscopes.

The Probe-Scope grows as you grow, giving you as many channels as you have USB ports; it’s almost infinitely expandable to tens (or more!) of channels. We are shooting for every channel to cost around $100, putting it on par or even cheaper than the commercial closed-source solutions out there today.

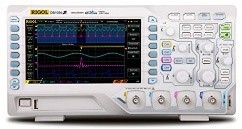

| Scope Model | Probe-Scope | RIGOL DS1054Z | Siglent SDS1052DL | Siglent SDS1202X-E | Hantek DSO4102C |

|---|---|---|---|---|---|

|

|

|

|

|

|

| Price/channel | $100 | $88 | $130 | $180 | $145 |

| Open Source? | Yes! | No | No | No | No |

| Bandwidth | 60MHz | 50MHz | 50MHz | 200MHz | 100MHz |

| Voltage Range | 300V Pk-Pk | 300V RMS | 300V RMS | 300V RMS | 300V RMS |

| Memory Depth (Per Channel) | 16Mpts | 3Mpts | 16kpts | 7Mpts | 20kpts |

| Vertical resolution | 8 bits | 8 bits | 8 bits | 8 bits | 8 bits |

| Rise time | <5 ns | 7 ns | 7 ns | 1.8 ns | 3.5 ns |

| Scope Model | Probe-Scope | Scope Fun | OpenScope MZ |

|---|---|---|---|

|

|

|

|

| Price/channel | $100 | $375 | $75 |

| Open Source? | Yes! | Yes | Software Only |

| Bandwidth | 60MHz | 100MHz* | 2MHz |

| Voltage Range | 300V Pk-Pk | 40V Pk-Pk | 40V Pk-Pk |

| Memory Depth (Per Channel) | 16Mpts | 64Mpts | 32kpts |

| Vertical resolution | 8 bits | 10 bits | 12 bits |

| Rise time | <5 ns | 3.5 ns | 175 ns |

*The Scope Fun has no anti-aliasing filter and therefore can give misleading results

Clearly, there is a large market gap for a low-cost, high-performance open-source instrument. This is the gap that the Probe-Scope is designed to fit in.

We have updates detailing every step of the design processes, everything from tricky design and analysis of high speed dividers to our process for laying out and assembling our boards.

We started with our detailed design and spreadsheets:

Then we moved on to a set of spread bench test PCBs to test all our subsystems:

And now we have our final PCBs hot off the press from PCBWay!

The hardware design is complete; our final PCBs were produced and assembled by PCBWay and functioned as expected right out of the box. We are planning on using the same design for volume manufacturing,...

Read more »They're here a day early!

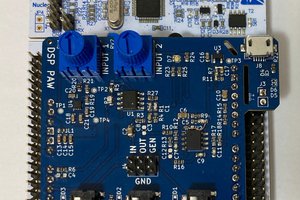

Our final boards came in this afternoon. Here's a closeup:

Kempton's making the cases for them now.

We've squashed the bugs and straightened out the kinks... Here's the first screenshot of real data coming in from the ADC! We use pyqtgraph for the data rendering, which performs excellently and has all the plotting and UI features we want baked right in, so we've avoided sinking a ton of time into displaying the waveform. Tomorrow we will add the actual units to the GUI and support setting the parameters of the device, and on Friday we'll have the real boards in our hands.

(disclaimer: we're driving the ADC directly with a function generator here, just for simplicity's sake)

(also disclaimer: we're not using a teensy and I don't know why Windows thinks it is one, only on this computer does it say that...)

As we mentioned a few weeks ago, we had hoped to post an update about the software by now. So where's it at? We haven't shared anything yet because we have a lot of moving pieces in this system (FPGA acquisition, FIFO, and sample output, PIC sample ingress, PIC USB comms and protocol, host comms and protocol, host GUI, and host measurement features), many of which are working quite well in and of themselves, but the product as a whole isn't quite ready to roll. We will be finishing it this week of course, and we're confident we will have something impressive to show off by Saturday.

We haven't been doing nothing, however: Aside from continually working on the software, we put together a demonstration unit and showed it off at the Microchip MASTERs conference about two weeks ago, along with a very early version of the software. Check it out:

And while it's not really relevant to what we're doing now, here's a neat short video I put together a while ago of us assembling the digital test board:

Finally, we just got word (and pictures!) from our PCBA vendor that our final boards have been assembled, so we'll get those in the next two or three days, just in time to show them off to you all in our final submission. Stay tuned!

We recently finished the layout of our final probe scope available on our github, now an obligatory PCB picture:

Here is an animation of how the Probe Scope stacks, to allow expanding to multiple channels all connected to one PC. The contacts on every Probe Scope distribute the trigger signal from the master Probe Scope to all the slave devices for synchronization.

We sent away the PCBs to our favorite PCB vender, PCBWay for assemble and fabrication.

In other news, we are working hard on the Digital Test Board, developing all the software. We hope to post an update at the beginning of next week.

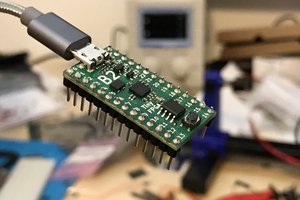

We recently got our PCBs in and built up, and having detailed the testing of the analog boards, it’s time to show off the Digital Test Board in its early stages. Unlike the analog boards, where the bulk of the work was done in designing them before they were made, this was straightforward to design and will take much more effort to program. So, expect some more updates over the weeks as all the software and firmware gets put together.

First, a glamour shot:

We need to get the final Probe-Scope board designed and sent out fairly soon, since the lead times for getting it made and assembled (and we will be getting it assembled) are pretty long due to the high density, and the competition deadline is approaching. So, to start off, we’re just verifying that all the pieces of the digital test board work so that we can be comfortable reusing those schematics in the final design. That means probing the ADC to make sure it’s outputting data (it is), loading code onto the PIC and FPGA to make sure they run with the correct clock sources, and then eventually (not done yet but soon) implementing a simple USB device on the PIC, and operating the HyperRAM with the FPGA.

The PIC was easy to get running as we have some lightweight test code we often reuse, and it works just fine with the external 24MHz oscillator (which is basically required for USB to work). The FPGA, on the other hand, was a bit more of a challenge for me as I have not used Lattice Diamond before, and its documentation is very spread out. Pro-tip: the file list has tabs at the bottom… you really want to check out the process tab. At any rate, I got that running too, clocked off the output of the ADC. Watch it all blink:

This leaves the USB and the RAM to be tested. The USB connections and clock, I’m not too worried about, they match known good designs. The RAM however, I’m also not too worried about, but it remains to be proven that our concept of clocking it at a higher speed using the FPGA’s PLL will work in this exact configuration. Stay tuned…

EDIT: The PLL for the RAM worked perfectly fine, thanks to the configurator it wasn't a pain at all.

Having recently received the parts and PCBs for all of our subsystem test boards, this post is one in a series detailing the buildup and testing of those boards. Today we’ll be showing off our Analog Frontend board, which includes the Variable Gain Amplifier (VGA) and Filter that makes the whole thing work. To start, here’s a picture of the finished board

After cursing the designer of the board (me), who decided that 0402 was the right size for most of the components, I finally got it assembled and up and running. One of the first things that I noticed was that it ran hot. In the back of my mind, I knew that the VGA (an ADRF6518) drew a lot of power (400mA at 3.3V or around 1.3W), but I didn’t quite consider the thermal implications of that. Checking the board with a thermal camera (shown below), the VGA got all the way up to around 70°C, which is actually right about the calculated value, but of course, I forgot to calculate it beforehand…

The first thing I did was write some Python scripts for my Raspberry Pi to control the ADRF6518 (over SPI), letting me play with its bandwidth and gain settings, along with controlling the MCP4728 DAC that set the Offset and Gain levels. Once I got it all set up and working, I connected it to our DG8SAQ VNA in order to get some frequency response plots, and they looked amazing! Here’s a picture of the board all hooked up for testing. I’m using a Tek P6248 differential probe (plugged in on the right) to feed the signal into the DG8SAQ.

Shown below is a screenshot of the results, with five sweeps at five different bandwidth settings, from 1MHz to 63MHz (the maximum setting).

As you can see, the gain is flatter than 0.5dB overall, and for individual settings it’s better than 0.1dB. And now here’s a screenshot zoomed all the way out, with the bandwidth set at 50MHz. To achieve an ENOB of 8 bits, we need at least 50dB of rejection at our Nyquist frequency (125MHz) in order to prevent aliasing. Here we get 80dB of rejection, well beyond the requirement.

The frontend was working so well, in fact, that I decided to test it at 63MHz (the maximum frequency of our VGA Filter) and we were able to get 65dB of rejection! Therefore, we can comfortably rate the Probe-Scope’s maximum bandwidth as 63MHz, surpassing our design goal of 50MHz.

You can find the schematics and layout for this board on our GitHub, or if you go back to an older project log, there’s a screenshot of it too. Next on the list is the Digital Test Board, which we’ll have a short post about just verifying its hardware up soon.

We just got in the parts and PCBs for all our test boards, so this will be the first of several posts on the testing and bring up of the boards.

The first board we built and tested is the Frontend Divider test board (for a detailed explanation of why this board is so complex and needs careful attention, see our previous post). Below is the assembled Frontend Divider board. It contains a 30x resistor divider with special layout considerations, a tuning capacitor to ensure a flat response, and the frontend buffer amplifier.

Ideally, we’ll be able to tune the divider so that the frequency response is very flat; in order to test that, I connected it up to our Bode 100 Vector Network Analyzer, a low-cost, (relatively) low bandwidth USB VNA. It can perform several measurements over a range of frequencies (from 1Hz to 50MHz), most importantly for us, it can measure Gain Magnitude, Gain Phase and Group Delay.

Here is a picture of the Frontend Divider board hooked up to the Bode 100… do ignore the mess.

After a bit of fiddling with the tuning capacitor’s value, I was greeted by this beautiful bode plot:

The gain is almost perfectly flat across the board, and while the constantly decreasing phase might instill some concern at first, that too is our desired outcome. (It’s what we want in order to get a constant group delay, which we’ll cover in detail in a future article.)

Here’s some more detailed plots of the Gain, Phase and Group Delay (shown as Gain Tg):

Now, in order to measure past 50MHz and fully understand the performance of our Frontend Divider, we need to switch to another instrument: the DG8SAQ VNA from SDR-Kits. The DG8SAQ is a low-cost VNA which can measure from 1kHz to 1.3GHz. I swept our fronted from 100kHz to 250MHz. You can see from the plots below that the Frontend Divider is not the bottleneck of the Probe-Scope; it actually has a bandwidth of more than 150MHZ!

For the curious readers, the Frontend Divider schematic is shown below, and as with everything we do, the source can be found on our Github.

Create an account to leave a comment. Already have an account? Log In.

Amazing design expertise and great presentation, good luck in the competition. I especially liked the front end discussion and flattening out the response to 50+ MHz. In the front end, you talk about 10x attenuation but settle on 30x in the next discussion with no discussion. Does the overall system noise get better or was it wanting to get to the 300v levels of the market comps? Beautiful work.

I am in the middle of a review of (1) Software Defined Radios (SDRs) being used for oscilloscopes, (2) Oscillioscopes being used as SDRs, (3) ADCs being used for both SDRs and oscilloscopes, (4) All sensors - as I have to come up with a policy for the Internet Foundation for sensors, instruments, data sharing, data networks, sensor networks.

My one comment. ALL the groups I have investigated who are building the kinds of devices you hope to offer, live and die by their user communities. NOT just the developers, but the much larger (usually a hundred fold) community of people who want to use devices for simple things, and for new things.

A. Make sure you can stream the data at full sampling rate to disk.

B. Make sure you can put the device on the Internet (TCP/IP or any channel) and let remote users and systems control it.

C. You are using high enough bandwidth, and processors speeds, you can serve several users at once. The SDRs on the Internet can be used by dozens of people at once. So multiplex your analog detectors and amplfiers and let your ADCs convert that, monitor and report on it, store and forward and stream it.

D, Hardware FFTs and statistical data streams for operations monitoring and applications. All the SDRS are spectrum analyzers. But they are very sophisticated and applying a wide range of detection methods. The whole field is getting more sophisticated, but there are some real stick in the muds too.

Is this available yet? How much? When? Still alpha testing? Beta testing? Where are you advertising and building communities?

Make little brother devices to get people to buy into your company and products. It won't be what you are trying to build for some purpose you have not clarified. But it could make sales and get you started. Yes, you have the price about right, but there are already a LOT of people in the game. if found some new things coming out of China today, while looking. They can make anything for a quarter of the price. What you can do it keep the user community, by helping people accomplish their goals. Hardware does not do that. Software does not do that. It comes from finding people and startups and new industries and helping them.

Adopt the people who make copies and sell hardware identical to what you offer. Their new users are your users. They will come to you for software, new methods, ideas, connections, and community.

Good luck

Richard Collins, The Internet Foundation

Good work! how do you synchronize more channels together?

Thanks!, we use Pogo pins and stacking in order to distribute trigger signals here is our update with a fancy gif of how they stack; https://hackaday.io/project/165964/log/166259

Hey guys, even though we were competition for the hackaday prize I love where your going with Probe-Scope. The formfactor and your specs are impressive.

Thanks! We put a lot of time into design, analysis and software.

Become a member to follow this project and never miss any updates

Jon Klein

Jon Klein

Jonas Norling

Jonas Norling

Luke Valenty

Luke Valenty

Clyne

Clyne

Is this project still being developed. Im really interrested since it would be incredible for field work but as the PC software is...quite primitive Im not really convinced. If you decide to develop the software further or maybe even get integration into some other software like Pulseview by Sigrok or a different ready made software