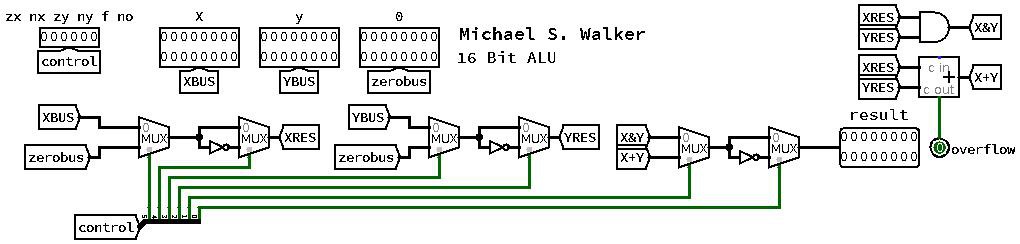

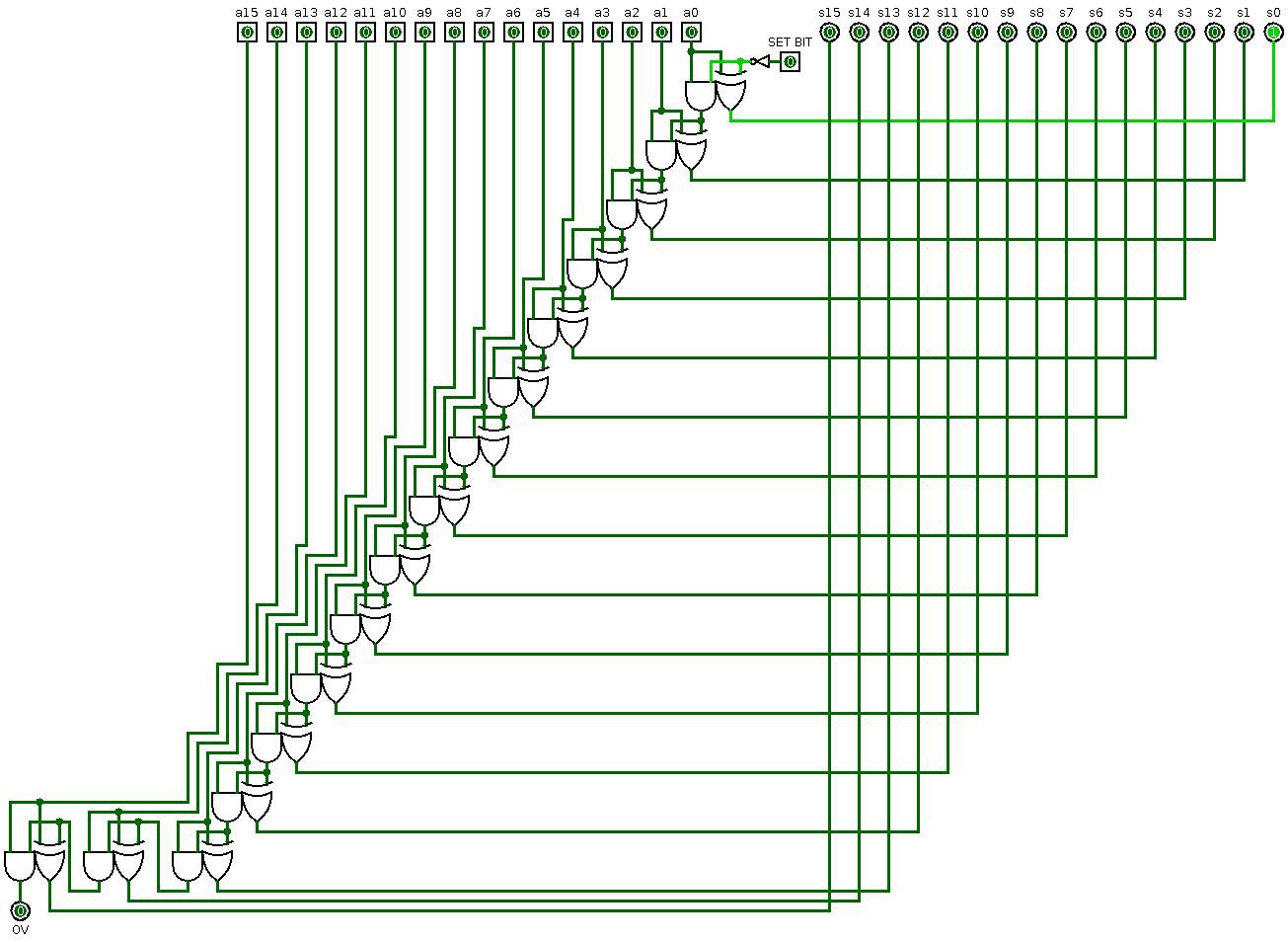

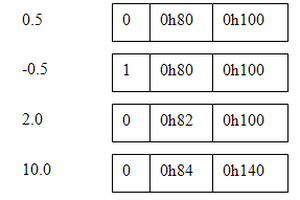

Stage 1) Boolean Logic & Arithmetic

Stage 2) Sequential Logic

Stage 3) Machine Language and Computer Architecture

Stage 4) Assembler

Stage 5) Stack Arithmetic, Program Control and high level language design.

Stage 6) Compiler syntax analysis and code generation.

Stage 7) Operating system.

Computer build from first principals

Complete computer build from the logic to the compiler and operating system.

Michael Walker

Michael Walker

kaimac

kaimac

Bruce Land

Bruce Land

Really nice, currently hacking on it as well. Using the book