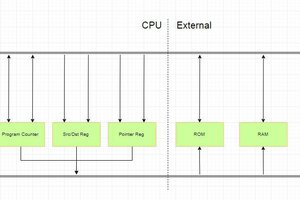

V2 objective

I got v1 working in the sim but then decided I wasn't going to build it in hardware as these very simple CPU's aren't that capable or complex and I wanted more of a challenge; something that would force me to learn more.

So this has changed out of all recognition.

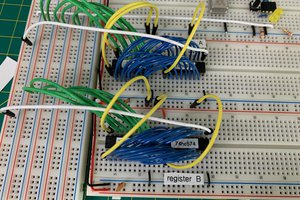

Along the way I got distrated by a hardware build of a testing device for all the chip's Ive bought for this CPU project. The testing device project can be found in my project list. That was interesting and a throw back to my Uni days in the 80's.

Now, I'm firmly back on the CPU task and nearing the end of the design and sim phase....

UPDATE: After a few more months I've finally settled on the capabilities and design and have arrived at an approach that appeals to my sense of symmetry. I've adopted some features of ARM; specifically conditional instructions and status flag control.

V1 objective

⭐️ I wanted to do things a little differently to some of the other efforts on the internet!

I wanted the assembler and any other code I write to to be more readily accessible and instantly usable to others (like you) without installing python or perl or whatever first, so I've written the assembler in google sheets!I want to be able to run at least the typical demo programs like Fibonacci

- I would like to extend it to play some kind of basic game (tbd)

- It will have an assembly language and assembler for it

- I might port C to it

- I want to simulate it first

- I want to build it physically, or a more likely a derivative

John Lonergan

John Lonergan

Wenting Zhang

Wenting Zhang

Dave Collins

Dave Collins

Brandon Reinhart

Brandon Reinhart

Thanks.

Want to get back to the hardware but I've been having some success porting the vbcc compiler to spam-1