[ edit: the instruction set has changed, see New Instruction Set ]

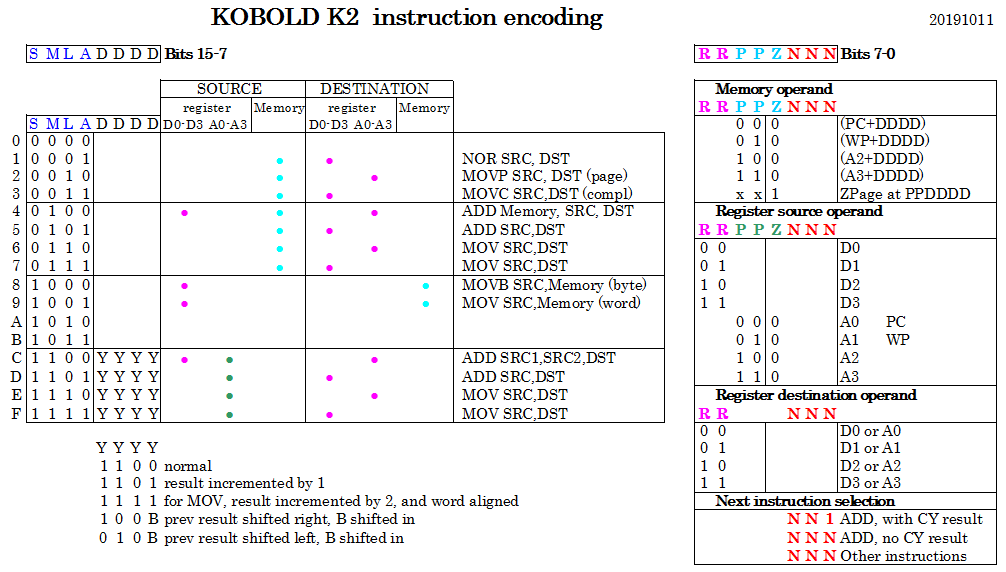

At the moment, this is the instruction encoding:

You get a bigger version when you click on it.

An instruction is 16 bits. The upper 8 bits are in the left part of the picture, and the lower 8 bits are in the right part. The upper 4 bits control almost directly the data path, and the other bits set displacement and register numbers.

CONDITIONAL BRANCHING

The CPU only supports branching on carry set. To be more precise, EVERY ADD instruction will do a branch on carry.

The branch must be within the same instruction block, and the branch target is the next slot as defined in NNN, but with the lowest bit set to one.

So what if we don't want to branch at all ? Then we put the next instruction in a slot with an odd number. If now the carry gets set, it will make the lowest bit of the next slot number one. But it is already one, so it will go to the same instruction, whatever the carry bit may be.

And what if we want to branch on NO-carry ? We simple change the positions of 'normal' next instruction and the jump target. This is possible, because instructions can be in any position within a block.

Note that jump-on-carry can also be used to test for zero. Just add 0xFFFF to the value that you want to test. If there is a carry, the value was not zero. The constant 0xFFFF will not cost us space for an immediate variable if we put it in the zero page space.

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.