Here is the new instruction set. It is quite conventional (thats my personal view), but has a few quirks due to the fact that a lot of functionality was pushed into the instruction set, while keeping the decoding circuits very simple.

I will present the new set in three encoding tables, starting with a few simple ones.

(There is also a colored instruction map available)

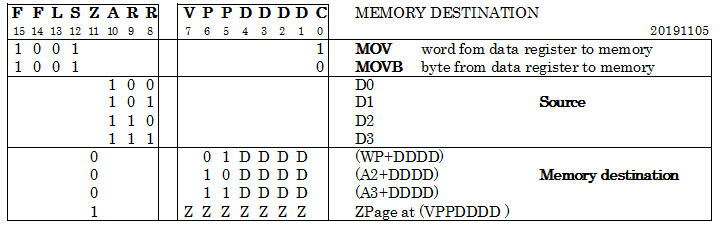

WRITE TO MEMORY

There are two ways to address memory:

- Pointer with displacement. WP, A2 and A3 can be used as pointer (PC should be used for reading only).

- Zero page. Zero page size is 128 words (256 bytes).

All four data registers can be written to memory, either as word or as byte. To write an address register to memory, first move it to a data register and then write it.

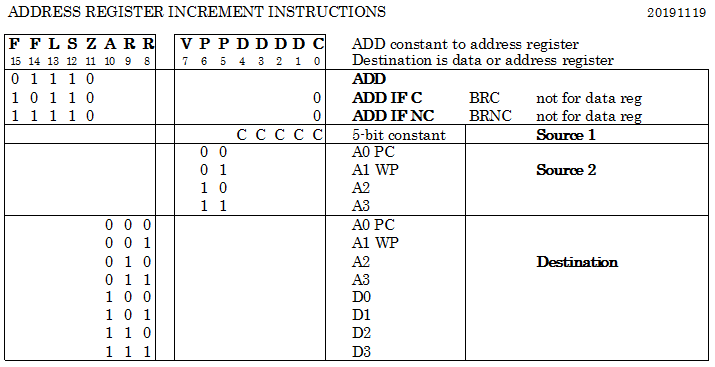

INCREMENT ADDRESS REGISTER

Address registers can be incremented with a value from 1 to 31. This can also be conditionally, mostly used in combination with A0 (PC). So the branches can skip 15 instructions at most. For greater distances, 16-bit immediate conditional jumps must be used. Note that the destination of the addition can also be a data register.

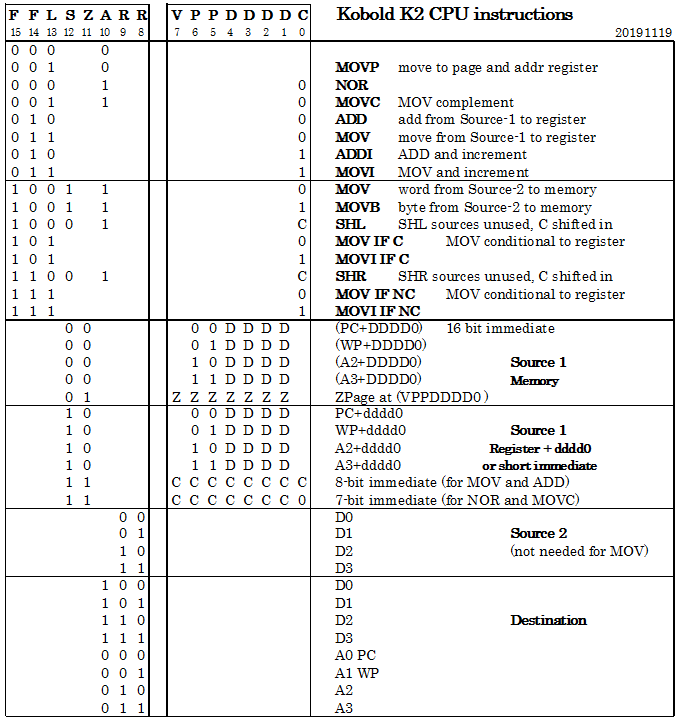

ALL INSTRUCTIONS

This may look a bit complex. But you just pick an instruction, one or two sources and a destination.

Note that there are several ways to specify the source operand:

- Address register indirect with displacement, (includes 16-bit immediate when addr register is PC)

- Zero page location

- Address register plus small (5 bit) constant

- short immediate (7 or 8 bit)

Oddities:

- The MOV to register instructions can be conditionally executed.

- A jump or branch is just a move or conditional move to the PC (register A0)

- There are MOV-with-increment instructions. One of its uses is incrementing a value in memory with just two instructions

- MOVI (value),D2 ; get value in D2 and increment it

- MOV D2,(value) ; store value back

- ADD-with-increment (ADDI) is just adding with the Carry-input of the ALU set. Useful for subtraction.

- For SUB, use MOVC (Move and complement) followed by ADDI (Add and increment)

- For AND and OR, use NOR in combination with COM (Complement) or MOVC (Move and complement). COM is the same as NOR with #0.

- For MOV (and ADD) with 8-bit immediate, the lowest immediate bit is formed by choosing between the MOV and MOVI instruction. The assembler will handle this. Since this lowest immediate bit is connected to the carry-input of the adder, it is not available for the logical functions NOR and MOVC.

- SHR instruction acts on the result of the previous instruction.

- The SHL instruction writes to memory as a side-effect. The assembler will use the highest zero-page word (at 0x00FE) as location to write to.

Remarks for address register destination:

- ADD instructions have 3 operands, the source-2 operand is always a data register, and the number of the source-2 data register must be the same as the number of the destination address register. So ADD A1, D2,A2 is possible but ADD A1, D2,A3 is not possible.

[ edit 20191115: I pushed some more functionality in the ISA, schematic in file section has been updated ]

[ edit 20191119: new schematic uploaded to file section ]

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.