In the last log we added conditional compilation flags that allow us to use other software builds. We were left with two undone tasks:

- Build the software

- Add 6850 emulation

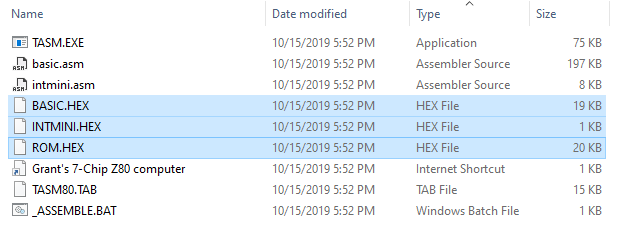

Let's tackle building the software. Grant's folder is a bit confusing since there are 3 .HEX files and we only need one file to create the image.

BASIC.HEX is the BASIC interpreter. INTMINI is a short interrupt handler for serial I/Ot that replaces the monitor code from the 9-chip design (which had both interrupt handler and monitor plus CP/M loader). ROM.HEX is the file that would be loaded into a ROM in the "real" design.

There's a couple of ways to get what we need out of this. One would be to compile the code. I was able to use TASM with my Windows 10 machine in an earlier log by running TASM under DOSBOX. There's also a newer TASM version which allows it to be assembled under Windows 10.

An easier way would be to use srec_cat to convert the .hex file to a C-Array. That is described in detail in this log. The command line is:

path_to_srecord\srec_cat ROM.hex -intel -o GS_7_CHIP_ROM.c -C-Array

That worked and created a C file with the following at the top:

/* http://srecord.sourceforge.net/ */

const unsigned char eprom[] =

{

0xF3, 0xC3, 0xB8, 0x00, 0xFF, 0xFF, 0xFF, 0xFF, 0xC3, 0x9F, 0x00, 0xFF,

0xFF, 0xFF, 0xFF, 0xFF, 0xC3, 0x74, 0x00, 0xFF, 0xFF, 0xFF, 0xFF, 0xFF,

...

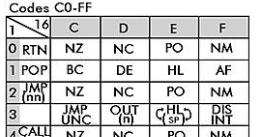

Chedking this code from the relevant Z80 Opcode chart:

Opcode 0xF3 is DIS INT (Disable Interrupts) and 0xC3 is JMP (jump). Grant's INTMINI has this code at the top.

;------------------------------------------------------------------------------

; Reset

RST00 DI ;Disable interrupts

JP INIT ;Initialize Hardware and go

;------------------------------------------------------------------------------

; TX a character over RS232

.ORG 0008H

RST08 JP TXA

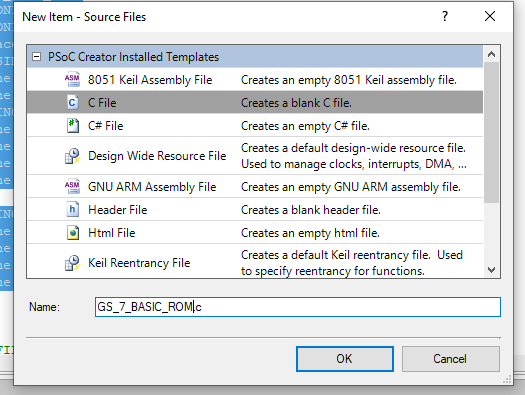

So, it looks like the code matches just fine. Next, add a new file to the PSOC project: calling it GS_7_BASIC_ROM.c which we will place the newly generated code into.

After dropping the file and making a few changes, the top of this file looks like:

#include "Hardware_Config.h"

#ifdef GRANT_7_CHIP_Z80

const unsigned char gs7chip_basic_eeprom[] =

{

0xF3, 0xC3, 0xB8, 0x00, 0xFF, 0xFF, 0xFF, 0xFF, 0xC3, 0x9F, 0x00, 0xFF,

We have the #define conditional compile that gets set by the Hardware_Config.h file. The fact that the new code is not greyed out indicates that it will be included in the next PSOC build that is done. The inserted #define requires a #endif at the end of the file to close it.

#define EPROM_FINISH 0x00002000

#define EPROM_LENGTH 0x00002000

#endif

/* [] END OF FILE */

The array is renamed to be a name specific to this build. We could name all of the builds the same thing but it might be possible in the future to include multiple builds and select the build to run in some manner, so by pressing different front panel switches, so we are making this build specific to allow that possibility. This does mean that we need to add to the SRAM loading software for each specific build.

That is done inside the function that loads the software in the ExtSRAM.c file.

////////////////////////////////////////////////////////////////////////////

// void loadSRAM(void) - Load the SRAM on the card with the ROM code

// Initial code build is monitor plus BASIC code

void loadSRAM(void)

{

uint32 charCount;

uint32 SRAMAddr = MONITOR_START;

volatile uint8 dataVal;

for (charCount = 0; charCount < MONITOR_LENGTH; charCount++)

{

#ifdef GRANT_9_CHIP_Z80

dataVal = monitor_basic_eprom[charCount];

#endif

#ifdef GRANT_7_CHIP_Z80

dataVal = gs7chip_basic_eeprom[charCount];

#endif

WriteExtSRAM(SRAMAddr,dataVal);

SRAMAddr++;

}

}

We also need to add the definition to the top of the ExtSRAM.c file:

#ifdef GRANT_9_CHIP_Z80

extern unsigned char monitor_basic_eprom[];

#endif

#ifdef GRANT_7_CHIP_Z80

extern unsigned char gs7chip_basic_eeprom[];

#endif

At this point the software builds in PSOC Creator but if we run it there will be no output.

In the next section, we will write the code to emulate the 6850 inside the PSoC.

land-boards.com

land-boards.com

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.