I am changing my earlier approach to the SPI Slave Select (SS) line.

The SPI controller should be used to control the SS line. But as we saw earlier there's times when that value needs to be over-ridden. During the initialization there needs to be at least 72 SPI clocks with SS and MOSI both high. It is a problem to have the PSoC SPI_Master to do since the interface wants to assert SS for the entire transfer. But we want to use the SPI_Master to control the SPI interface under other circumstances.

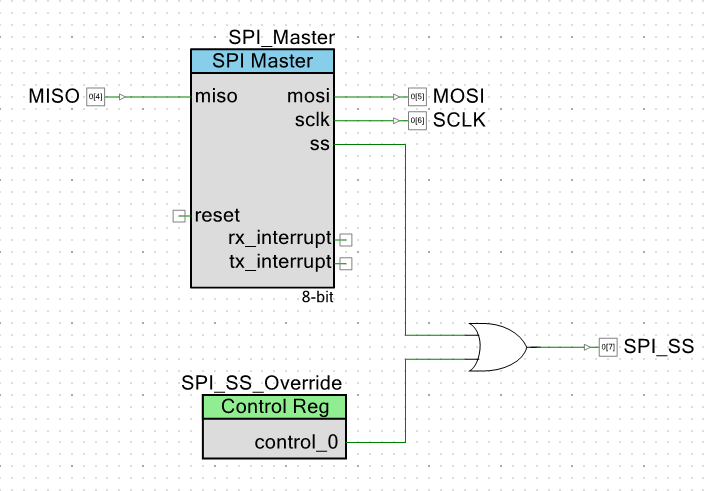

Here is a way to achieve both of these goals.

The extra OR gate on the output lets the SPI_SS_Override control register over-ride the active-low Slave Select from the SPI_Master during just the initialization phase. Setting the bit to 1 will cause the SPI_SS pin to have a 1 overrides the SS from the SPI_Master. Setting the bit to 0 after the initialization cycle allows the SPI_Master to control the line normally.

The extra OR gate on the output lets the SPI_SS_Override control register over-ride the active-low Slave Select from the SPI_Master during just the initialization phase. Setting the bit to 1 will cause the SPI_SS pin to have a 1 overrides the SS from the SPI_Master. Setting the bit to 0 after the initialization cycle allows the SPI_Master to control the line normally. This is one example of the flexibility of the PSoC approach. It's pretty easy to add hardware assistance to functions that would otherwise require more CPU attention.

land-boards.com

land-boards.com

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.