In a TTL type CPU, there is a need for two rising edges of the clock clearly separated:

- One rising edge to trigger the decode of the microinstruction and set the action signals

- One rising edge to trigger the action itself (update the register, etc)

Most TTL cpus use a single clock with an inverted signal to produce two rising edges per clock cycle (one from the clock signal, one from the inverted clock signal).

However, this might be playing dangerously as there are chances that one rising edge happens while the other clock signal is still active, creating situations that are very difficult to trace.

So one alternative would be to clearly separate the two signals with absolutely no overlaping time.

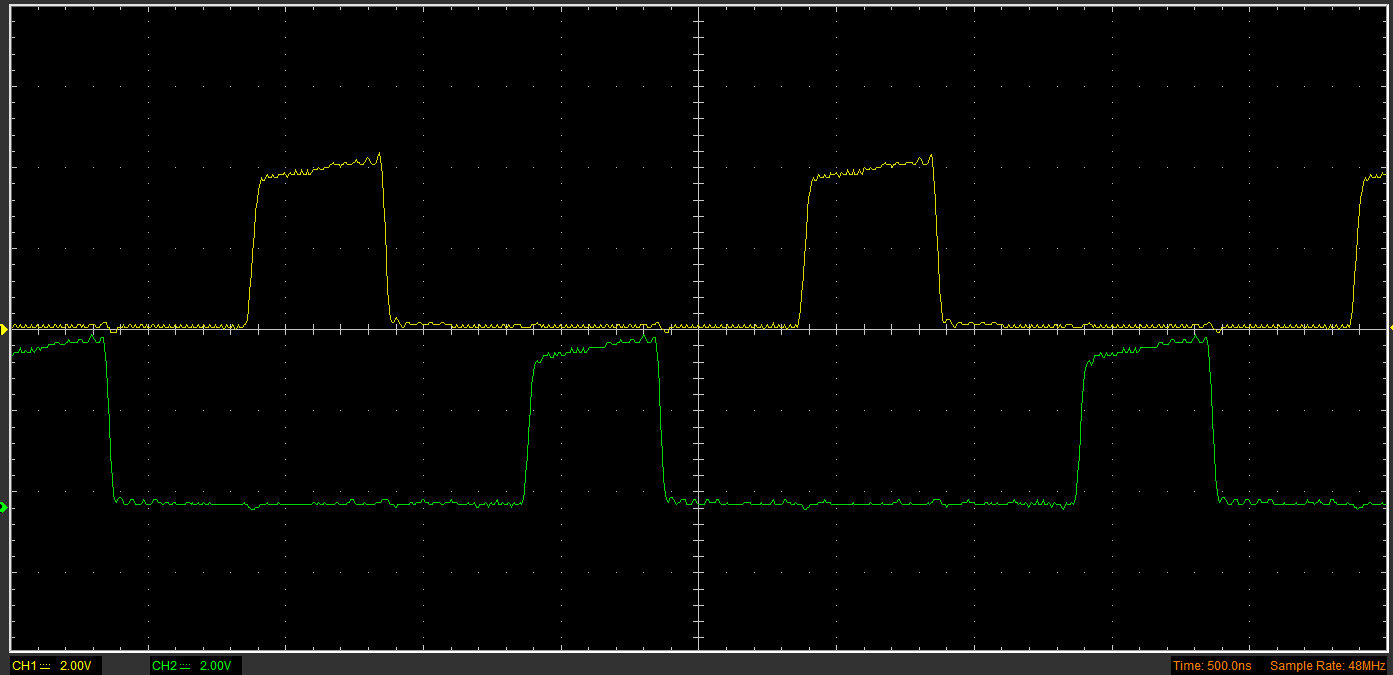

Here is an example (all screenshots with a 1 Mhz input clock signals from a quartz oscillator):

In such a situation, a rising edge can never happen at the same time than the other signal is active.

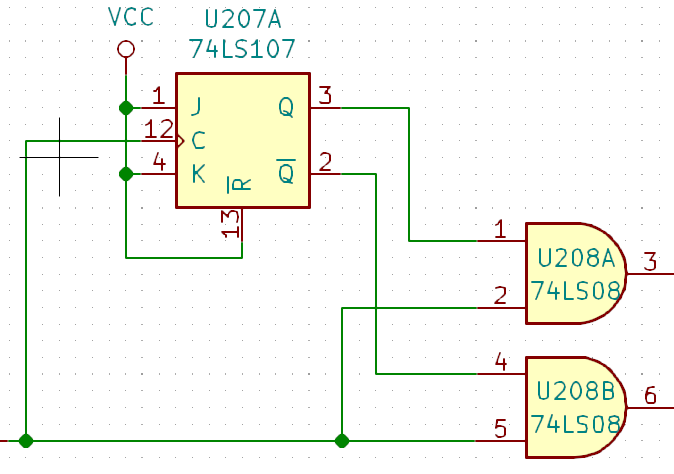

So how can you build such a signal ? Lets look at this simple circuit and analyze what is going on:

Lets input a clock on the JK flip-flop (pin 12). The JK is set with two active J and K signals, meaning that it will toggle its exits (Q at pin 3, inverse Q at pin 2) at each clock signal. Note that the 74LS107 triggers on the falling edge.

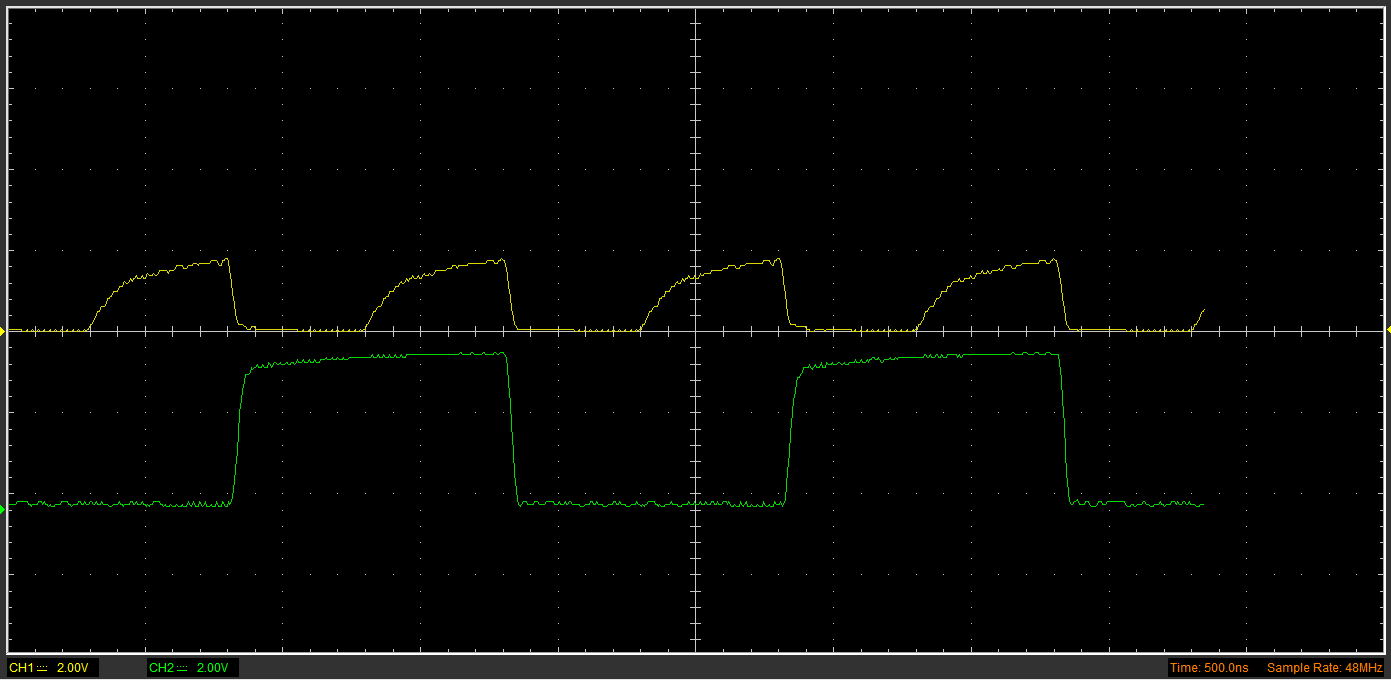

Below is the clock signal (pin 12 of the 74LS107, top signal) and the Q output (pin 3 of the 74LS107, bottom signal).

At each falling edge, the J-K flip flop toggles. It is therefore a frequency divider by 2. The output is half the frequency of the clock with a 50% duty cycle (ratio between high and low duration).

What happens then if we AND the clock and the Q output ?

Below is the graph of the clock signal (pin 12 of the 74LS107, top signal) and the output of the AND gate (pin 3 of the 74LS08, bottom signal):

We get the high part of the clock signal but only once out of two.

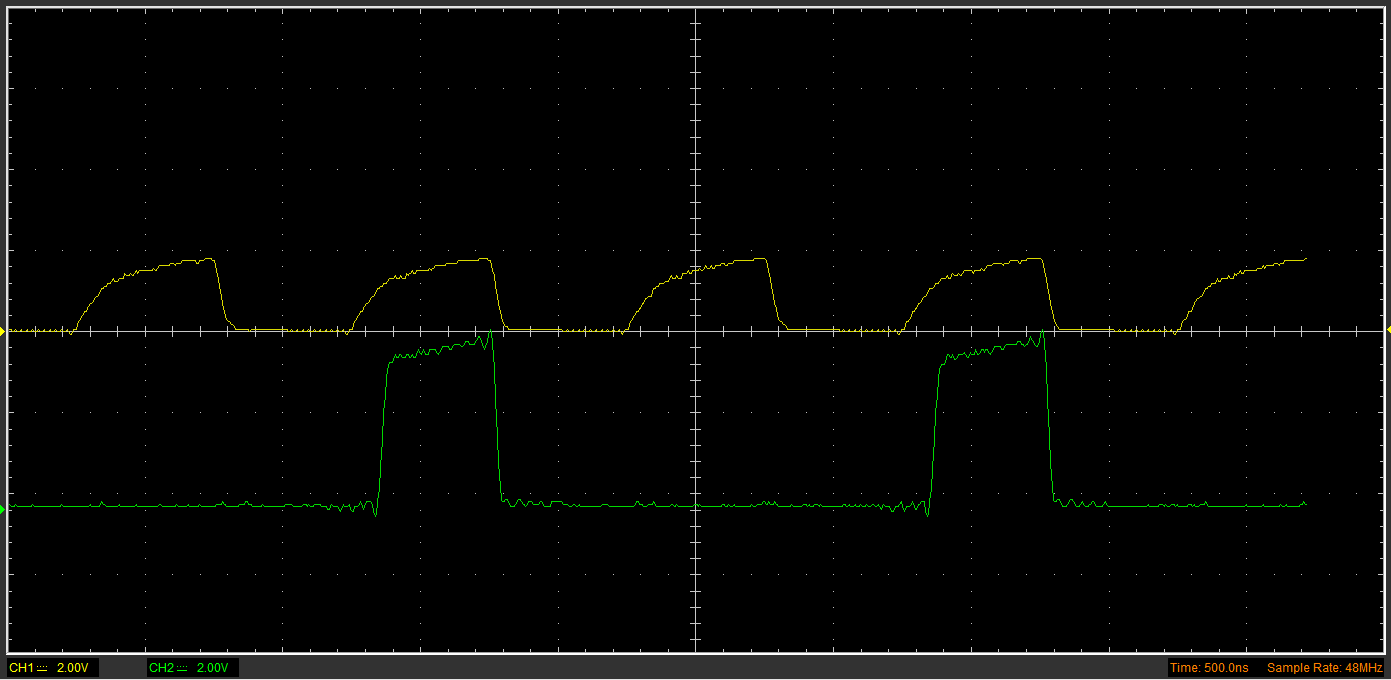

If at the same time, we AND the clock and the inverse Q we get the two reciprocating signals.

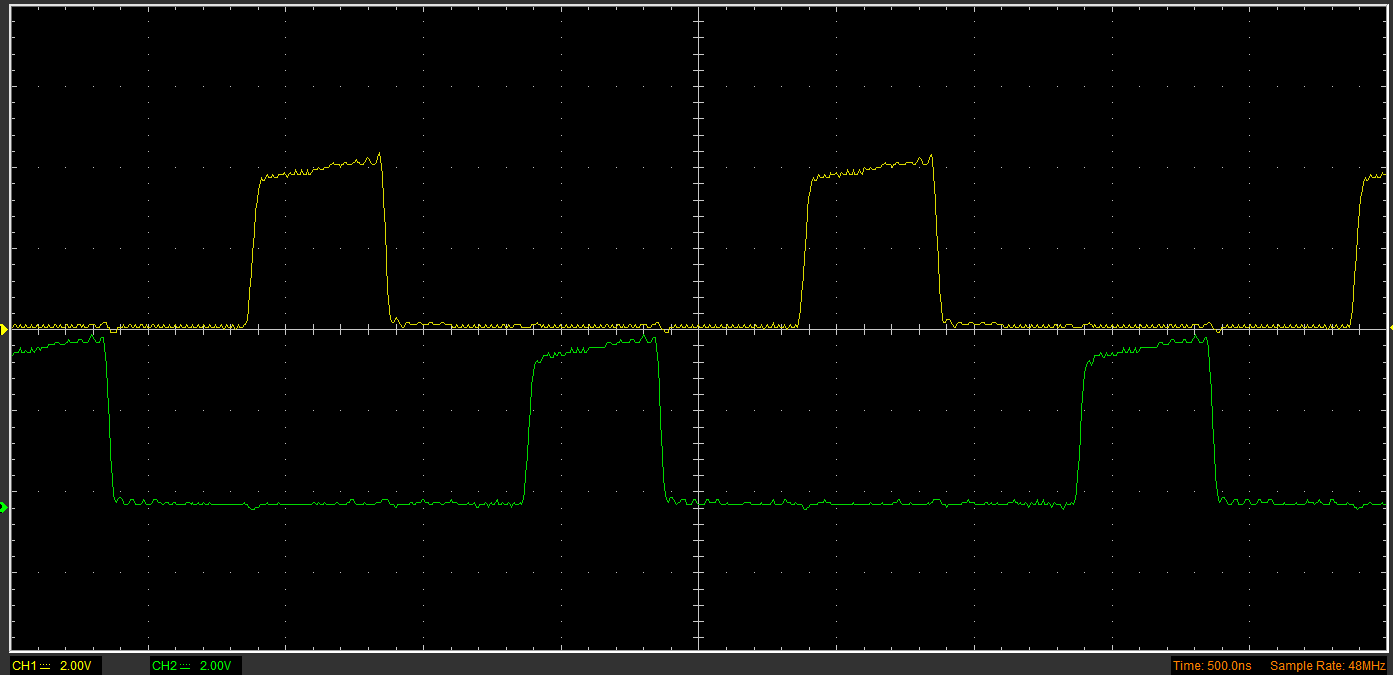

Below is the output of both AND gates (pin 3 of the 74LS08, top signal and pin 6 of the 74LS08, bottom signal) :

With such 2 clock signals, no chances that you will get a rising edge at the same time the other signal is high. The drawback however is that the clock is now half the frequency.

Ced

Ced

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.