One issue with @matseng's circuit is the sampling of the inputs: it will miss pulses shorter than the sampling period (10 or 5µs). Faster sampling means more CPU load yet no garantee to catch that 50ns spike that may happen. Sampling theory in all its glory...

The solution is on the hardware side.

I have examined how the input signal could create a longer pulse (>10µs) but the analog circuit becomes too quirky quickly. I want a very high impendance (to catch any "phantom" signal) and no constant RC time (to run at arbitrary speeds). I don't want to change or tune an analog part whenever I change the sapling rate.

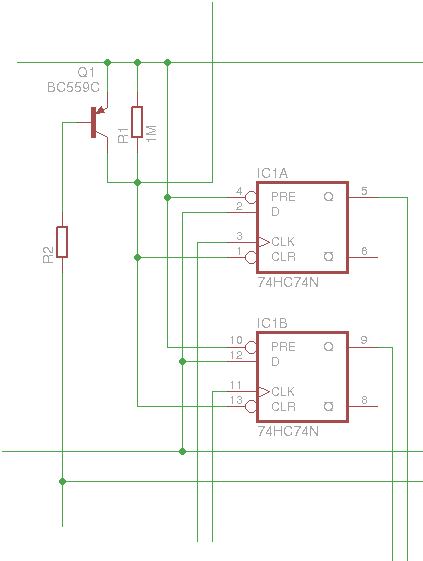

My solution uses full digital CMOS : the 74HC74. It's better to use an integrated Set/Reset latch because a discrete version (with transistors or 74HC00 gates) will work slower and might miss very short events.

The events are asynchronous so the sampled signal is tied to the asynchronous /SET input (active low, so there must be a pull-up resistor). Then after the sampling, the latch must be reset: the Data input is tied to 0V and the synchronous clear signal is tied to CLK.

There is still a small but non-zero chance that a short event arrives during the clear transition. There is some uncertainty about the behaviour in this case and more importantly, it's hard to copy the latched value at exactly the same time as it is being cleared.

The solution is overlapped sampling : both latches of the 74HC74 are used but with shifted clocks.

Of course, all events will be seen as a half-sampling-period longer but no event that can be sensed will be missed. And it works at any sampling frequency (within the datasheet's specified range).

For the sensing itself, the IC's pins are used directly. A 1M pull-up keeps the signal from floating and the very high value creates a reasonable RC time. If we consider the pins and traces to have about 10pF of capacitance, a short-to-0V event will be stretched to a few microseconds.

The 1M pull-up is shorted on demand by a PNP transistor. This follows a discussion on #ReTest - Relay timing tester's comments: dry vs wet contacts. R2 is selected to give about 100mA current in the transistor to simulate a full load.

20161108: Following suggestions, due to unavailable stock and for better speed, I got some SN74AC74N. It's rated for pretty high speed so it won't miss a 10 or 5ns pulse.

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

Great solution

Are you sure? yes | no