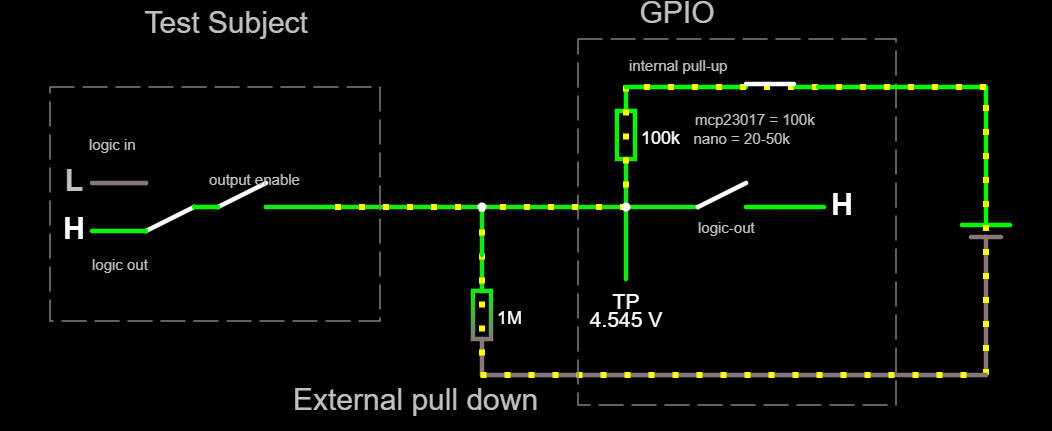

I use currently dedicate two GPIO pins per test pin in this device and this allows me to distinguish between 1/0 and Z outputs.

I was wondering if I'd missed a trick, and whether I could have done this reliably with only one pin plus a pull down resistor.

See simulation .. http://tinyurl.com/usm9eqd

Firtsly, I don't think this idea works at all if I want to support TTL because I need an external pull down resistor who's value is able to pull-down a high-Z line but without interfering with reading a high logic level. That means we need a high value.

However if we use a very high resistance for the pull-down then the input low leakage current (out) of the devices will ensure that we are not able to achieve a 0.8v low anymore.

However if we use a low value then this will pull down the line so much that we can't achieve a valid logic high.

This page explains pullup/down value selection and the problems associated with poor choices https://www.electronics-tutorials.ws/logic/pull-up-resistor.html (recomended).

Turns out the max pull-down for TTL is 2k !! This is assuming an input leakage current of 400uA and a max valid low threshold of 0.8v Eg 74LS245 is 200uA

By contrast the MCP23017 has Input a leakage current of 1uA , 74HCT is 0.1uA, ATmega328p is 1uA which might allow for a pull down of something like 800k perhaps.

However, even 800k would probably pull the logic high down to 4.4v and since this device is already pushing it a bit with voltage levels I'm not keen on taking a device that I've found reliable in testing and then making it flakey.

So - no after all.

John Lonergan

John Lonergan

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.