One nasty part of this kind of design is to drive the pass gates with non overlapping pulses. Otherwise it's a terrible mess...

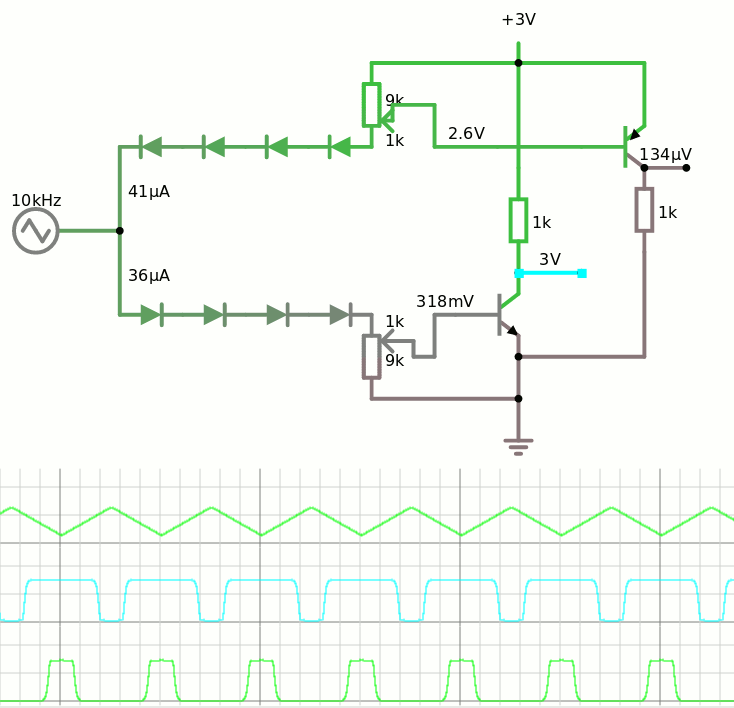

I have found this simple complementary driving system, using only a pair of transistors, and a bunch of diodes. The cool part is where the duty cycle (and pulse width) is determined by a potentiometer, and there is no capacitor in sight so it should work at medium speed without problem. The input signal is also supposed to have a slope...

There is still some freedom in the choice of the number of diodes and the value of the potentiometers, though make sure that there are enough diodes to prevent a direct current from Vcc to GND ;-) At 3V the minimum would be 6 diodes.

The 1K pull resistor would be the actual load (2K2 resistors with each a BJT base and stuff).

I believe this driver would drive the first divide-by-4 cell. This cell would then output 2 non-complementary non-overlapping signals, suitable to drive the slower clocks. A divide-by-4 cell has 4 states and 2 BJT can detect two of the opposite states...

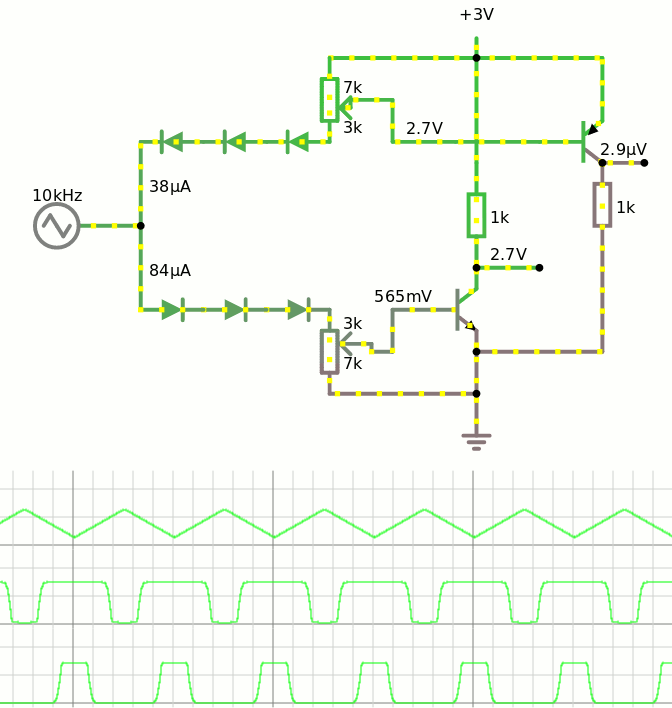

The version with 6 diodes works quite well too:

But now the shape of the input signal is the next critical problem.

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.