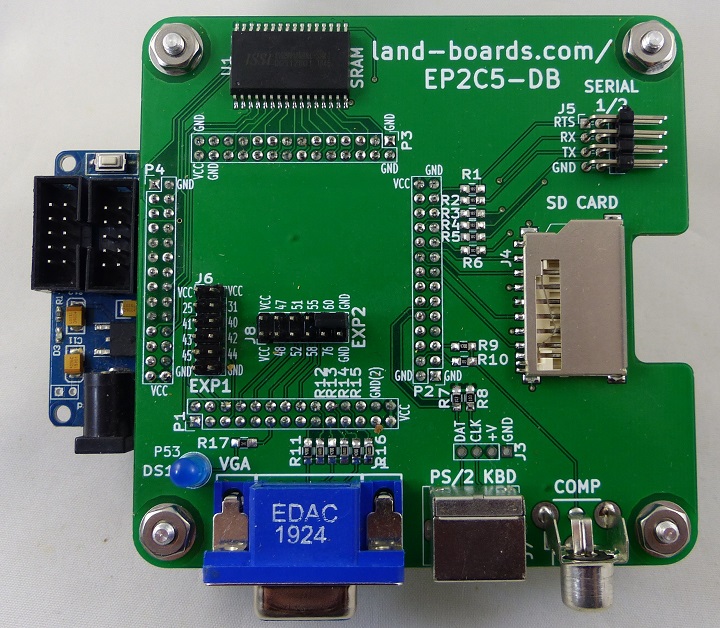

Earlier, I got MIKBUG running on one of the inexpensive FPGA cards mounted to my EP2C5-DB.

The board has 128KB of SRAM (only 32 KB are usable by MIKBUG). While I was waiting for SRAM chips I wondered if I could get MIKBUG working on the FPGA without external SRAM. Of course the capabilities would be limited to the Internal SRAM in the FPGA. Ther EP2C5 FPGA has are 26 blocks of 512 bytes for a total of 13K of SRAM.

MIKBUG goes from 0xC000-0xC8D5 which is 4KB of SRAM or 8 blocks of 512 bytes.

I still wanted to keep the internal ANSI terminal for convenience but that can be reduced in size by eliminating the extended character set. Even with that, the ANSI terminal uses 10 of the 26 memory blocks of 512 bytes. The top of this has the vectors at 0xFFF8-0xFFFF. Th space is replicate 4 times by ignoring address bits A12 and A13 in the memory decoder.

The SMITHSBUG version of MIKBUG needs 128 bytes of SRAM from 0x7F00 to 0x7FFF. Since the smallest block is 512 bytes that would means there will need to be 512 bytes of SRAM from 0x7E00-0x7FFF. The equation for the address select is:

w_SP_RAM_CS <= (not w_cpuAddress(15)) and w_cpuAddress(14) and w_cpuAddress(13) and w_cpuAddress(12) and w_cpuAddress(11) and w_cpuAddress(10) and w_cpuAddress(9);

This leaves 7 blocks for SRAM or 3.5KB. This gives SRAm from 0x0000-0x0BFF. The equations for the chip selects are:

w_RAM_CS_1 <= (not w_cpuAddress(15)) and (not w_cpuAddress(14)) and (not w_cpuAddress(13)) and (not w_cpuAddress(12)) and (not w_cpuAddress(11));

w_RAM_CS_2 <= (not w_cpuAddress(15)) and (not w_cpuAddress(14)) and (not w_cpuAddress(13)) and (not w_cpuAddress(12)) and w_cpuAddress(11) and (not w_cpuAddress(10));

w_RAM_CS_3 <= (not w_cpuAddress(15)) and (not w_cpuAddress(14)) and (not w_cpuAddress(13)) and (not w_cpuAddress(12)) and (not w_cpuAddress(11)) and w_cpuAddress(10) and (not w_cpuAddress(9));

The data multiplexer into the CPU is:

-- ____________________________________________________________________________________

-- CPU Read Data multiplexer

w_cpuDataIn <=

w_romData when (w_cpuAddress(15) = '1') and (w_cpuAddress(14) = '1') else

w_ramData1 when w_RAM_CS_1 = '1' else

w_ramData2 when w_RAM_CS_2 = '1' else

w_ramData3 when w_RAM_CS_3 = '1' else

w_SPRamData when w_SP_RAM_CS = '1' else

w_if1DataOut when w_n_if1CS = '0' else

w_if2DataOut when w_n_if2CS = '0' else

x"FF";

Dumping memory shows it worked.

0BF0 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

................

0C00 FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF

................

land-boards.com

land-boards.com

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.