After installing the new 74LVC8T245 level shifters into the circuit and reprogramming the FPGA to drive the DIR pin (which I've labeled A_B, because I can never remember which side of the bus is driving when it's high or low), I'm happy to report that the RC2014 booted fine.

I dropped into MBASIC from CP/M, and typed the following:

OUT 110,0:OUT 111,99 OUT 110,2:OUT 111,87 OUT 110,3:OUT 111,12 OUT 110,22:OUT 111,&h78

First line tells the VDC-II that there are 100 characters in a complete scanline. The second tells the VDC-II where the start of the HSYNC pulse resides on the scanline. The third sets the HSYNC pulse width. Finally, the fourth tells the VDC-II that there are 8 pixels per displayed character with no inter-character fill.

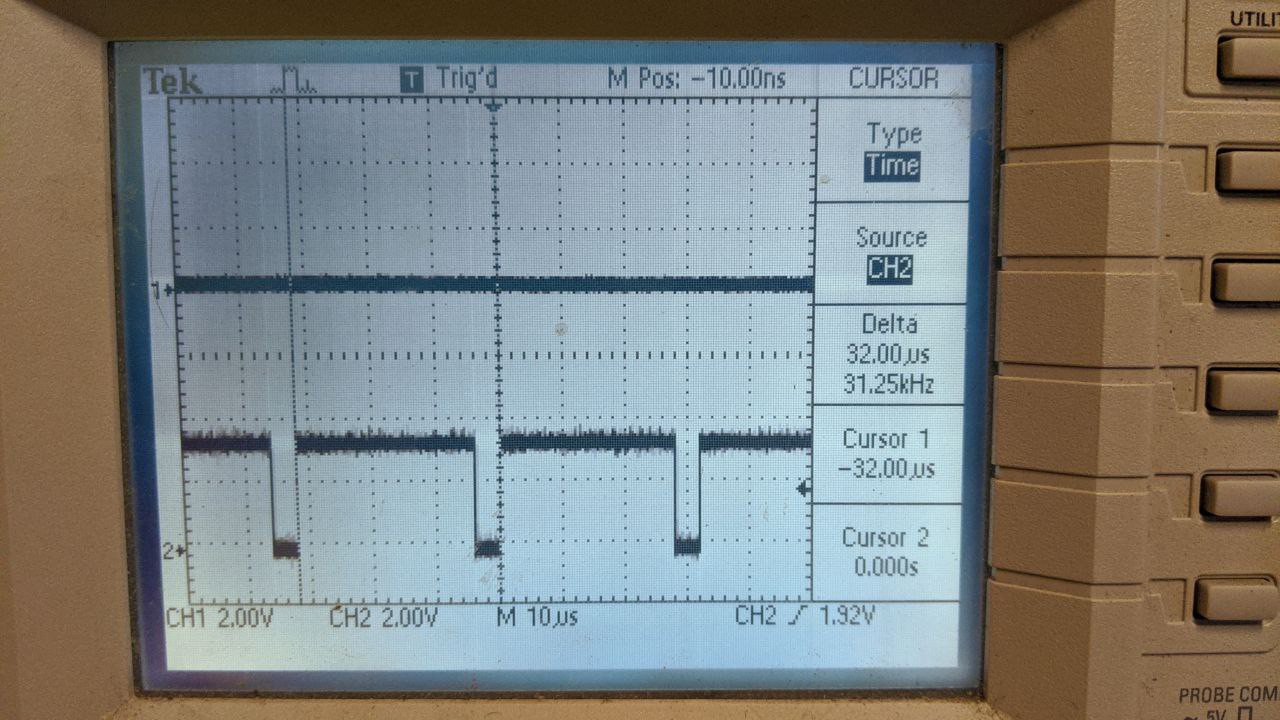

And I was immediate greeted with the following display on the oscilloscope:

This tells me several things all at once:

- You can interface to a Z80-compatible bus using 3-flop synchronizers clocked at 3.3x the Z80 bus frequency, without needing a dedicated bus clock input.

- TXS/TXB-type level shifters are not the correct type of level shifters to drive any kind of real bus, backplane or otherwise. They seem to be most useful for point-to-point circuits only; but, then, those are exactly the kind of links where not having a direction control is not a useful advantage to have. It's not clear to me what market TXS/TXB level shifters are intending to penetrate.

- 74LVC8T245 chips are powerful enough to drive a Mack truck, and fast enough to keep up with a Ferrari. Just make sure you set the DIR pin correctly.

- I really can solder SMT components without specialized equipment.

- nMigen rocks. TinyFPGA BX rocks. Based on my experiences with these tools, you can bet I'll try building more ambitious projects with this gear in the future.

Samuel A. Falvo II

Samuel A. Falvo II

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.