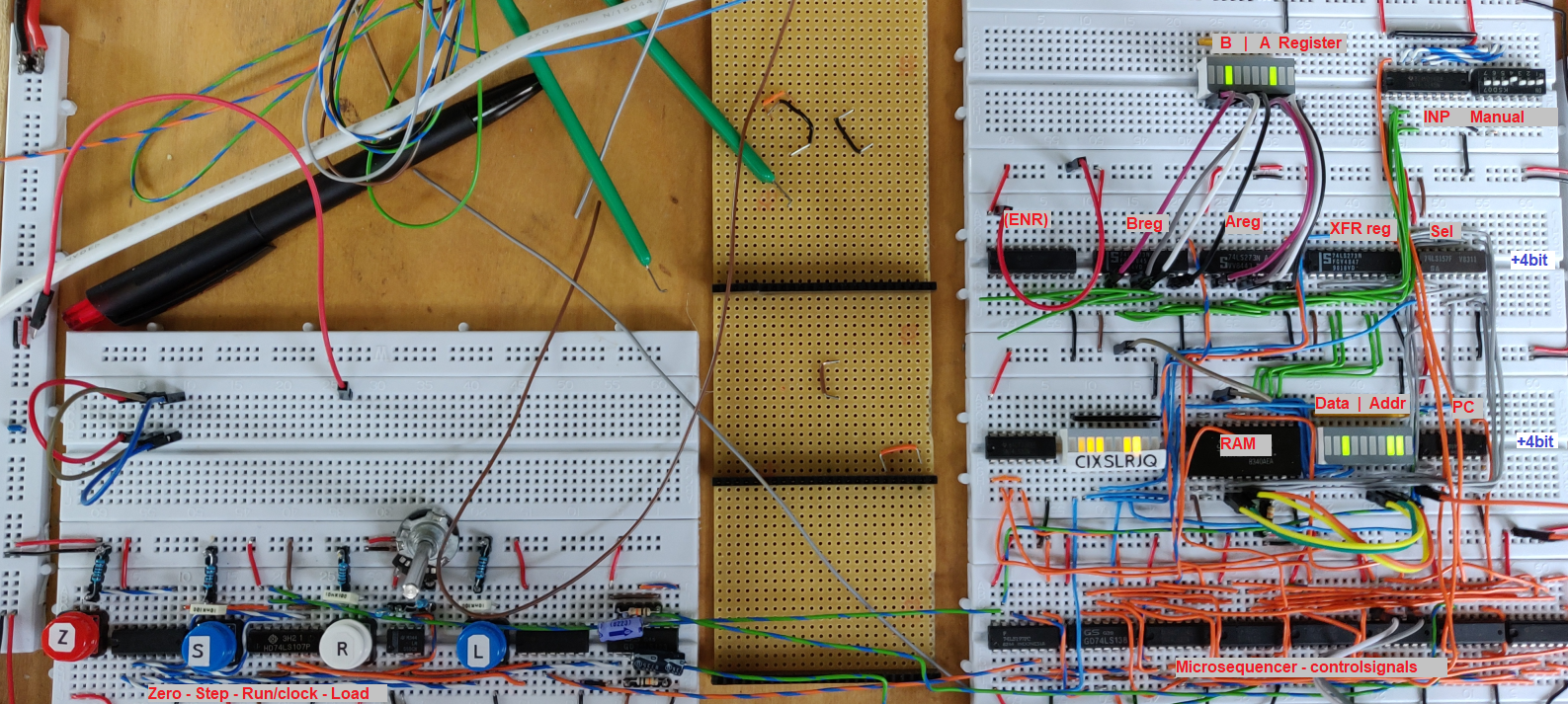

Progress is getting easier. I now have the XFR register working, and verified that indirect addressing works. YEAH! There was a debugging session - now that I needed to load the RAM with data, I discovered that the data was not loaded in the correct address. Finally (with a help of a Saleae logic analyzer) I had that Doh! moment - the monostable generating the LD1/2 pulses (you can see the capacitors on the picture) was wired wrong and fired LD1 and 2 at the same time, instead of after each other. Now the manual load works as advertised

Then there was a challenge with the PC jumping ahead 3 adresses when going from 7 to 8 - it turned out the LoadCounter line was floating (the LDP signal is not hooked up yet). It proves again that ALL inputlines to a chip must be tied High/Low if they do not have a signal. Of course I knew that, I was just being lazy/forgetfull/optimistic.

Hooking up the A and B registers was trivial, and the readout is temporary, just to convince myself that I load them with the indirected content.

Next is placing the ALU, where A/B display is. I'll use the '283 simple adder, and inverters to make it a subtraction - 2 chips (4 for 8bit wide. Note the room reserved for extending SEL and PC when going from 4 to 8bit). The LEQ detection is challenging me trying to minimize chipcount to do it.

It is getting tight on breadboard space. (I have more of them, but I'd rather not) Planning to move the INP and (not yet constructed) OUT unit to the left. That places all human I/O on the left, and right is Internal, I thus will use the "bus" (the strip board i the middle), and it is planned to have LEDs on it, too, so that removes one of LED bars. I had sort of semi-planned not to use "bus" in SUBLEQ ("only" ENR and INP (and RAMdata) are tristate) but that's the fun or point of doing a project like this - challenging the loosly laid plans to deliver in RealLife.

Michael Möller

Michael Möller

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

Just noticed your progress on a TTL computer and wanted to say congratulations, and thanks for documenting what you have so far! I'm interested in starting my own project like this. I was curious how you implemented or plan to implement the "ZER" line from your diagram. Is this a comparison or somehow derived from the subtraction operation itself?

Are you sure? yes | no