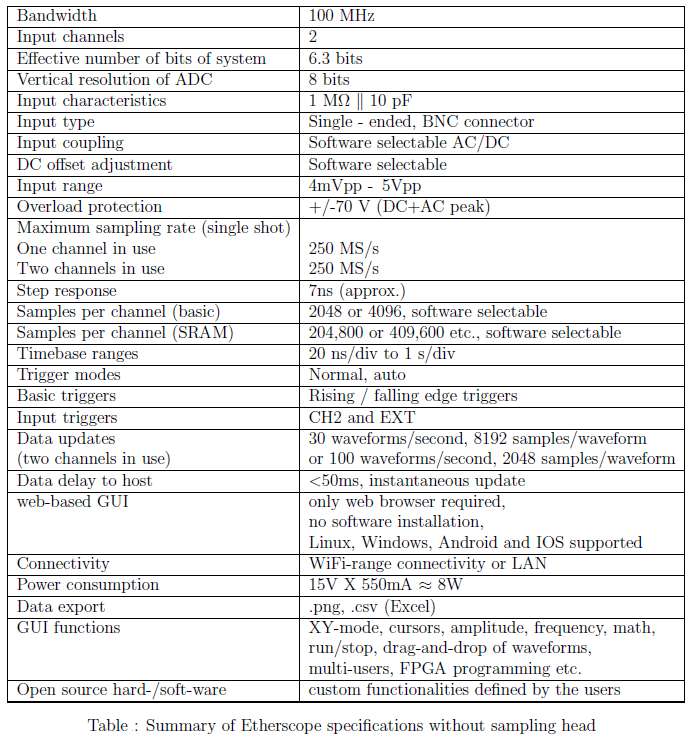

Part - I Real-Time oscilloscope

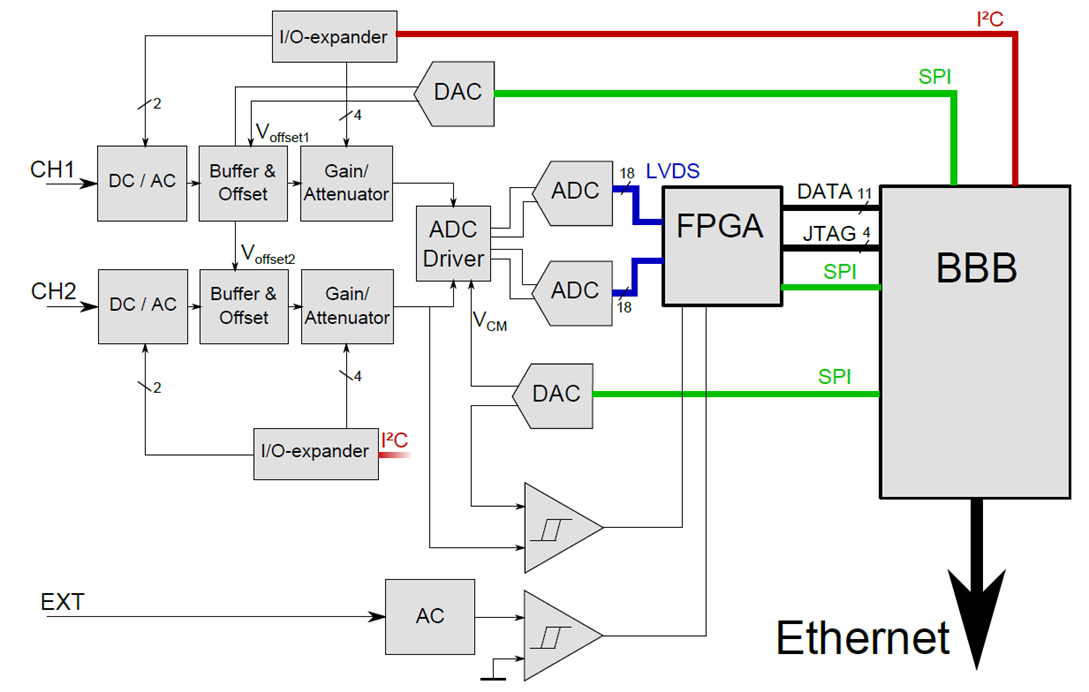

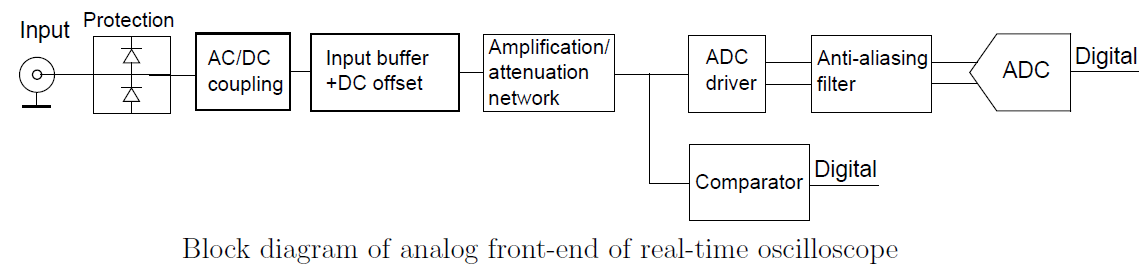

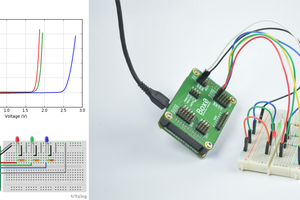

A. Analog front-end and ADC

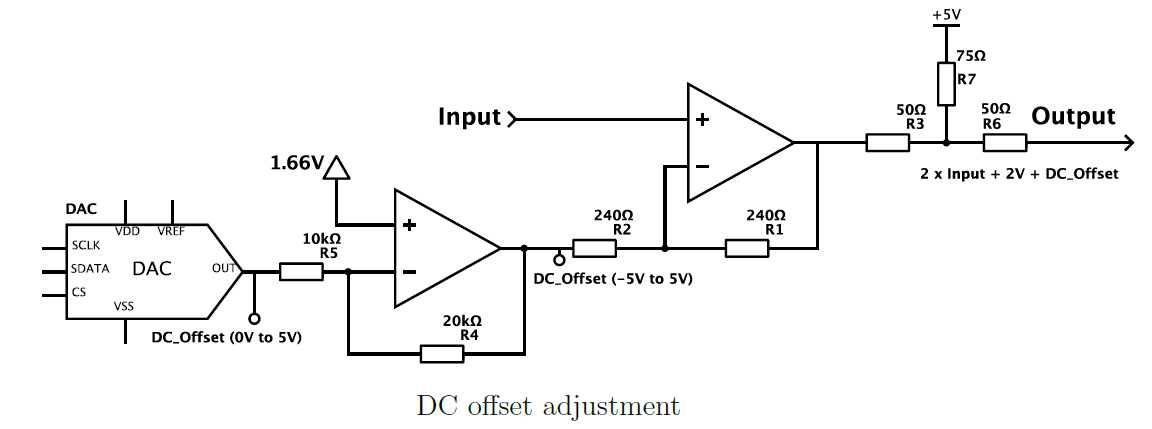

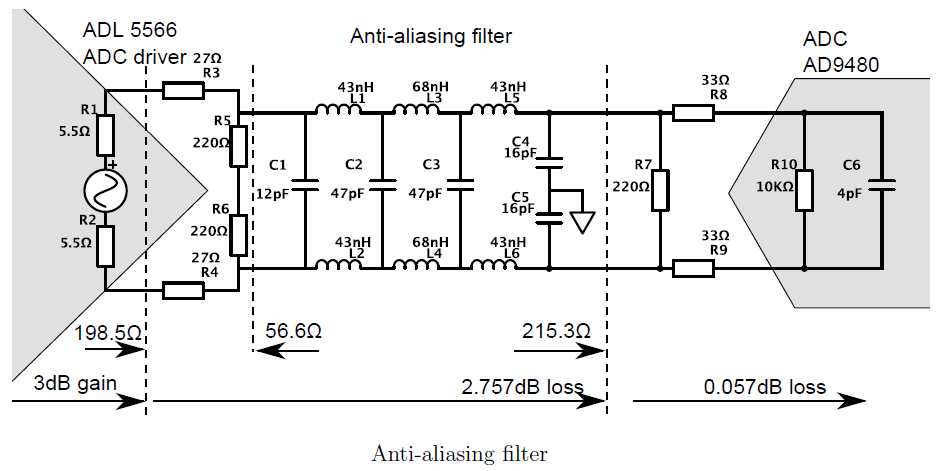

The input circuit features an input impedance of 1 M || 10pF and overvoltage protection. The DC/AC selection, DC offset adjustment, gain/attenuation (vertical division), trigger source selection etc. are supported by the ebbased GUI (graphical user interface). An 8-bit, monolithic analog-to-digital converter (ADC) converts the analog signals to LVDS (Low-voltage differential signaling) digital outputs at a sampling rate of 250 MS/s. A seventh-order Butterworth anti-aliasing filter is implemented between ADC driver and ADC, aiming to eliminate unwanted, spurious out-of-band signals.

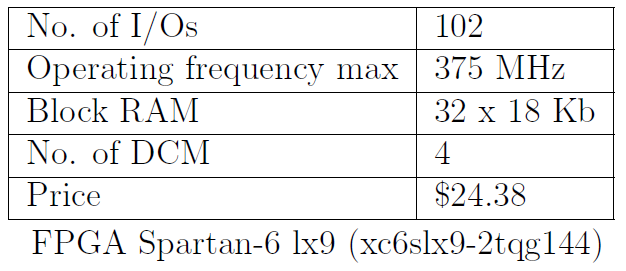

B. FPGA

Spartan -6 FPGA delivers an optimal balance of low risk, low cost, and low power for cost-sensitive applications. The FPGA can have abundant Block RAMs as data buffer or FIFO (First in, first out) to store the data acquired by the ADCs and abundant IOs (LVDS IOs) making it possible to handle the ADC LVDS outputs in parallel, and to make a fast, parallel communication link with the PRU (Programmable Real-Time Unit). The paramount aspect of an FPGA is the parallelism, which implies that the communication with Beaglebone Black, the interfacing of ADCs and the data transfer to PRU can be performed simultaneously. This unique aspect ensures the high performance and robustness of the system.

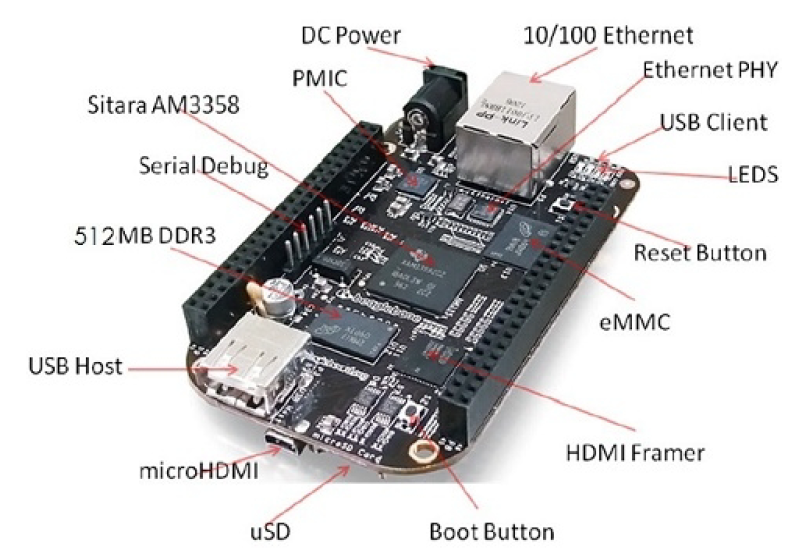

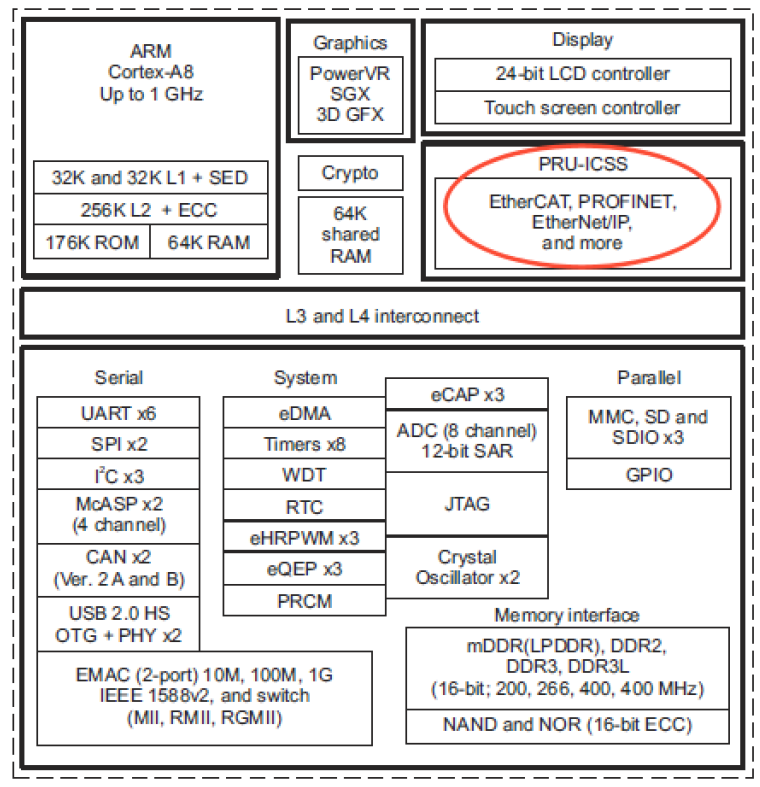

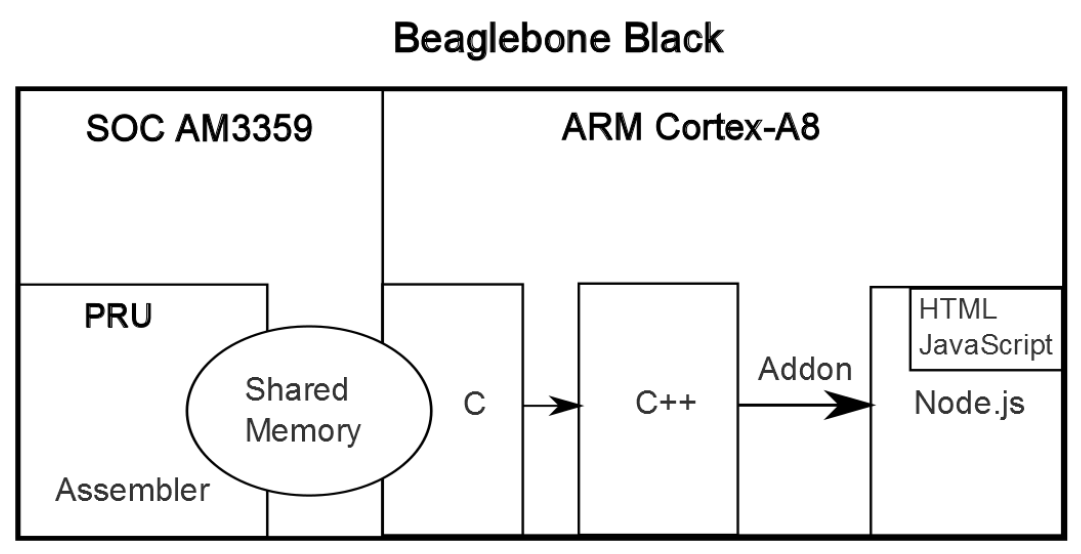

C. Beaglebone Black and PRU

The BeagleBone Black, newest member of the BeagleBoard family, is a credit-card sized, low-power, openhardware computer. It is community-supported development platform for developers and hobbyist and it runs on Linux and boots under 10 seconds. Unlike other similar devices, it does offer good access to most PRU or microcontroller pins, as required for hardware extension. The Programmable Real-Time Unit and Industrial Communication Subsystem (PRU-ICSS, embedded in Beaglebone Black processor) consists of dual 32-bit RISC cores (Programmable Real-Time Units, or PRUs), shared memories, and instruction memories etc. The PRUs can operate independently or in coordination with each other and can also work in coordination with the device-level host CPU, making it possible to set up a custom and independent communication link with FPGA.

D. Web-based software

The GUI is embedded in a dynamic web page (programmed in HTML and JavaScript) with the help of

Node.js library. This Node.js application is designed not only to maximize the throughput and efficiency but also to avoid the difficulty and complexity. This web-based GUI is supported by different web browsers on different operating systems and devices without the need for extra

plug-ins and troublesome software installation. The users have full control over the analog front-end with the help of this web-based GUI. Most control functions are accessible by drag-and-drop with a mouse (or stylus when using a smartphone), and via a web page even the FPGA can be programmed.

D.1. FPGA data to PRU

Generally, neither PRU nor FPGAs are developed to communicate with each other efficiently. They even use different languages in our design: the FPGA is programmed in VHDL, the PRU in C and assembler. Thus, interfacing the two can be a challenge. First of all, FPGAs do not have dedicated logic for communicating with PRUs or microcontrollers. So a suitable logic module must be designed from scratch. Secondly, the communication between the PRU and FPGA is asynchronous. So special care is needed to resynchronize the PRU to the FPGA clock domain. Finally, there is an issue of bottlenecks, both at the interface and on the PRU bus. Transferring information between the PRU and the FPGA usually requires cycles on the PRU bus and usually ties up the resource (PIO) used to effect the transfer.

Care must be taken to avoid bottlenecks with external RAM (if external RAM is needed). In our design, correct data transfer is guaranteed by a custom parallel communication...

Read more »

Kuldeep Singh Dhaka

Kuldeep Singh Dhaka

Keri Szafir

Keri Szafir

MagicWolfi

MagicWolfi