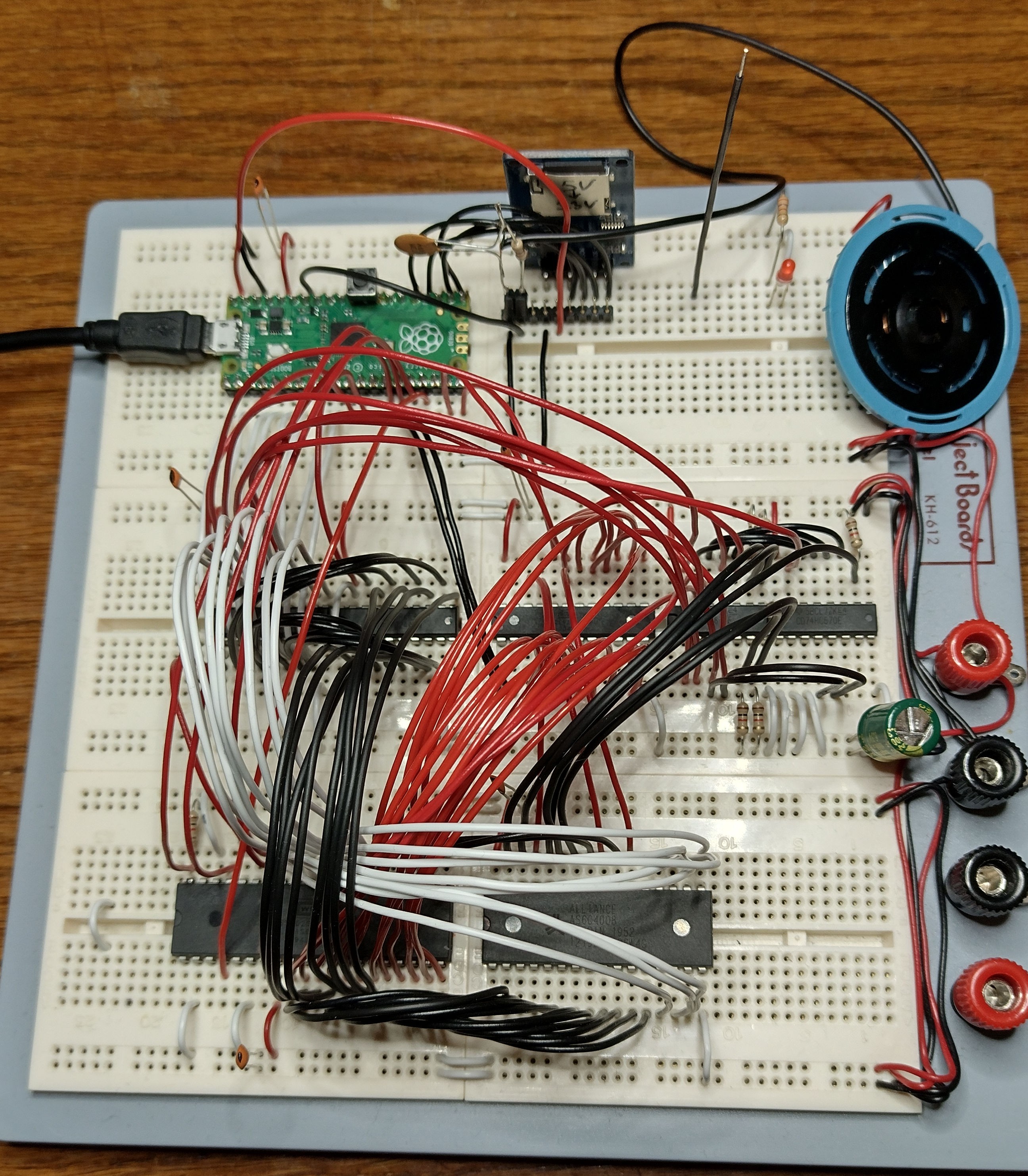

Here is my finished version of the CPLD-based HW. Works really well, using a CPLD to manage RAM-access and decode the different memory ranges. The Pico has much less to do and only needs to read the add/data if an I/O-operation is happening. This results in more than twice the speed compared to the PCB-version with buffers only.

This is clearly the way I would like to move ahead, with an ATF1504 CPLD as only glue logic between RAM, 65C02 and Pico. Due to the global chip shortage this will not happen any time soon, so I will shelf this proof of concept until sometime in the future when we can buy the chips we want,

Quick BOM:

- ATF22LV10C CPLD

- 74HC670 x2 for bank switching

- 74LVC244 for reading low byte of address

- 74LVC245 to read/write data byte

- 65C02 CPU

- 512KiB SRAM

- Pico acting as a complete and smart I/O-solution plus top-page ROM

- SD-card holder

- small speaker for SID-sound output

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.