-

MMU?

10/23/2023 at 16:06 • 0 commentsI've been unable to work on PZ1 for some time, but now I'm active again.

My latest experiment is to add io-protection, where only kernel code can access the io-area. This will make it harder (impossible?) for user processes to crash other processes. Of course it costs some cpu cycles to do kernel calls instead of using direct io, but I felt it was interesting to see what hardware is needed and how much overhead there is.

I have just gotten the first working implementation running, where basic starts and can do normal stuff, but pokes directly to the io-area does nothing. WOHOO!

-

Fuzix lives!

09/18/2022 at 05:42 • 0 commentsThis morning I logged in to Fuzix and got the first fortune-cookie.

Thanks to the help of Alan Cox, I can now run Fuzix on real PZ1 hardware as well as emulated courtesy of the RC2014 emulator. Feels great!

Now I have a ton of work ahead to understand more of how Fuzix works.

FUZIX version 0.4pre1 Copyright (c) 1988-2002 by H.F.Bower, D.Braun, S.Nitschke, H.Peraza Copyright (c) 1997-2001 by Arcady Schekochikhin, Adriano C. R. da Cunha Copyright (c) 2013-2015 Will Sowerbutts Copyright (c) 2014-2022 Alan Cox Devboot 512kB total RAM, 448kB available to processes (15 processes max) Enabling interrupts ... ok. Mounting root fs (root_dev=0, ro): OK Starting /init init version 0.9.0ac#1 Checking root file system. Current date is Sun 2022-09-18 Enter new date: Current time is 7:17:04 Enter new time: ^ ^ n n Fuzix 0.3.1 >@< Welcome to Fuzix m m login: root Welcome to FUZIX. # -

CPLD take 2

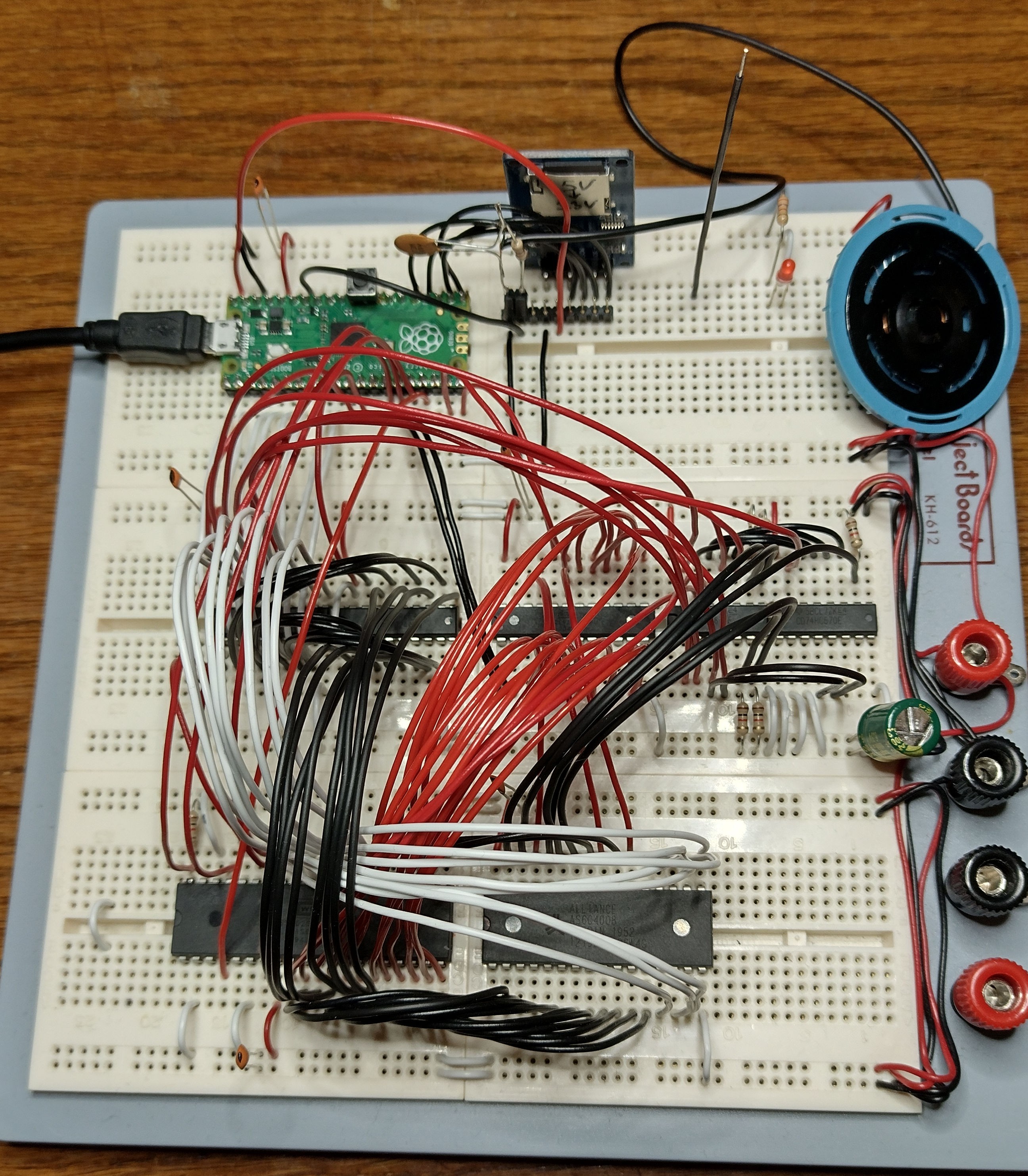

08/10/2022 at 18:48 • 0 commentsHere is my finished version of the CPLD-based HW. Works really well, using a CPLD to manage RAM-access and decode the different memory ranges. The Pico has much less to do and only needs to read the add/data if an I/O-operation is happening. This results in more than twice the speed compared to the PCB-version with buffers only.

This is clearly the way I would like to move ahead, with an ATF1504 CPLD as only glue logic between RAM, 65C02 and Pico. Due to the global chip shortage this will not happen any time soon, so I will shelf this proof of concept until sometime in the future when we can buy the chips we want,

Quick BOM:

- ATF22LV10C CPLD

- 74HC670 x2 for bank switching

- 74LVC244 for reading low byte of address

- 74LVC245 to read/write data byte

- 65C02 CPU

- 512KiB SRAM

- Pico acting as a complete and smart I/O-solution plus top-page ROM

- SD-card holder

- small speaker for SID-sound output![]()

-

Different take

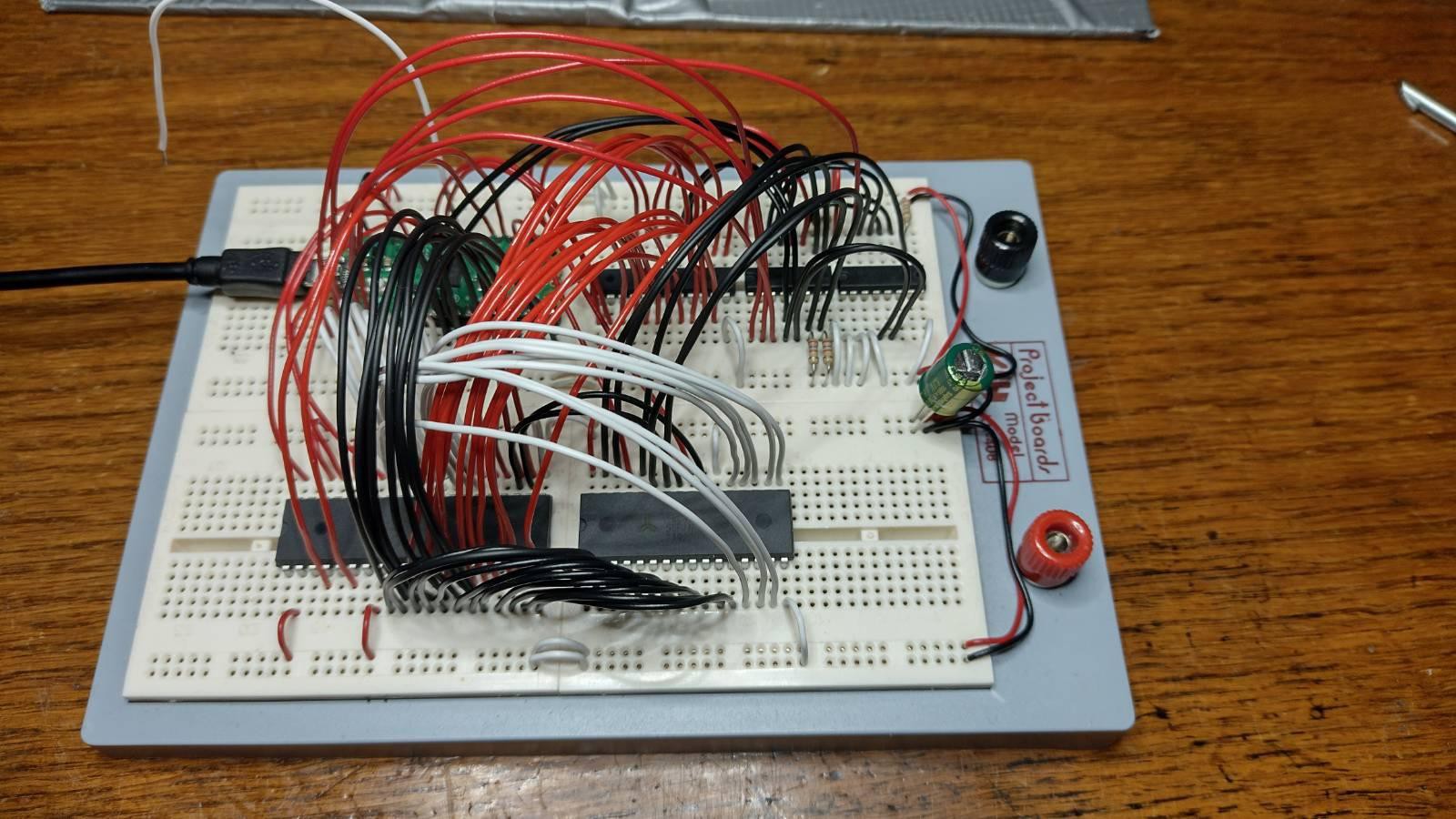

08/06/2022 at 06:32 • 0 commentsI was not satisfied with the performance of the previous version of PZ1_Pico, too many cycles were spent driving memory. So I went in the direction of CPLD to see how far that would take me.

It turns out quite far. With an unbuffered addr/data interface and an overclocked Pico, I could run the 65C02 @8MHz on the rats nest pictured below! The CPLD (ATF22LV10) performs RAM timing/decoding and there are 2x 74HC670 to deal with banked memory. The Pico handles top page ROM duty as well as all I/O-devices implemented. It also drives the CLK of the 65C02.

I REALLY didn't expect this to work at these speeds! I thought the 74HC670:s and the bread board would be big hurdles to reach much more than 2MHz, but I was obviously wrong.

This is not the final result, I've already built a version that adds 2 buffers for the data/addr so it is possible to get the number of used Pico-pins down to only 16 for interfacing with the 65C02 and CPLD. That leaves 10 gpio for all the I/O I want to drive, just like on the PCB-version. That is an even messier rats nest that will not show up in this post :)

There is a major problem with this implementation: the global chip shortage has most CPLDs I've looked at in severe scarcity. I have a few chips that I can make my prototypes with, but I couldn't build any more if I wanted to.

![]()

-

Optimizations and a new HW revision

07/19/2022 at 08:12 • 0 commentsI've been trying out different ways of optimizing the code to maximize the headroom for more HW-blocks in the Pico, and in doing that I happened to read the datasheet of the SRAM. There are 2 ways of controlling the read/write cycle, and I used the more traditional with CS tied to ground, WE & OE controlled by 2 separate signals from a 74LVC373. The 373 register was needed because the Pico has too few gpio pins. The other way of controlling the read/write cycle is to tie OE to gnd, WE to R/W of the 65C02 and use CS to tell when a read OR write cycle is occuring, saving a gpio pin.

I repurposed the SYNC-pin from the Pico that I didn't use anyway and now control the SRAM directly without going through the register (which takes extra time).

4 lifted legs and 3 soldered wires is all it took to mod the circuit, no cut traces.The SW has also been reorganized some to enhance the performance a bit further.

All in all, I went from 18500/20000 down to 14900/20000 with all these changes. Well worth it!

Now I just have to document it all and respin the schematic and layout before ordering new PCBs. Or maybe wait for further inspirations to pop up...

-

PZ1_pico 2.0

07/17/2022 at 07:12 • 0 commentsA second release of the Pico code is now ready on GitHub. No HW changes have been made, the PCB I ordered actually works!

This time I use my scheduler to multitask and manage the 512KiB RAM properly. Nothing new functionally compared to the Teensy-version of PZ1, only a proper port to the Pico-version. I use the second core on the Pico for sound :D

-

Holiday update

07/04/2022 at 17:23 • 0 commentsOn holiday, but still coding in a few spare timeslots :)

The added SD-card reader works, files on FAT16/32 can be used now.

EhBasic with multitasking starts, still needs some more testing.

65C02 runs @1MHz with everything enabled on 133MHz Pico. SID emulation and mixing at 44100Hz, no filters. Only core 0 used so far. PIOs could probably be used to offload a significant amount of load by reading/writing the buffers.

Looking bright!

Now all the work left to get this up to snuff for a GitHub release.

-

Live on GitHub

06/25/2022 at 09:16 • 1 commentThe PZ1_Pico project is now available at GitHub: https://github.com/NollKollTroll/PZ1_Pico

-

It works!

06/23/2022 at 06:49 • 0 commentsI wrote some low-level tests to make sure the buffers worked properly before implementing the simplest system. A version of EhBasic running in 16KiB ROM (in the Pico) and 48KiB of the external SRAM with one serial port via the Pico USB connection. Runs at a bit faster than 2.5MHz without optimizations or overclocking of the Pico.

I didn't think I'd get it correct on the first try, but the PCB really works as intended, YAY!

I'll wrap it all up neatly and make a decent Github repository of code/PCB/docs before going back to porting Fuzix.

-

Real HW, Pico edition

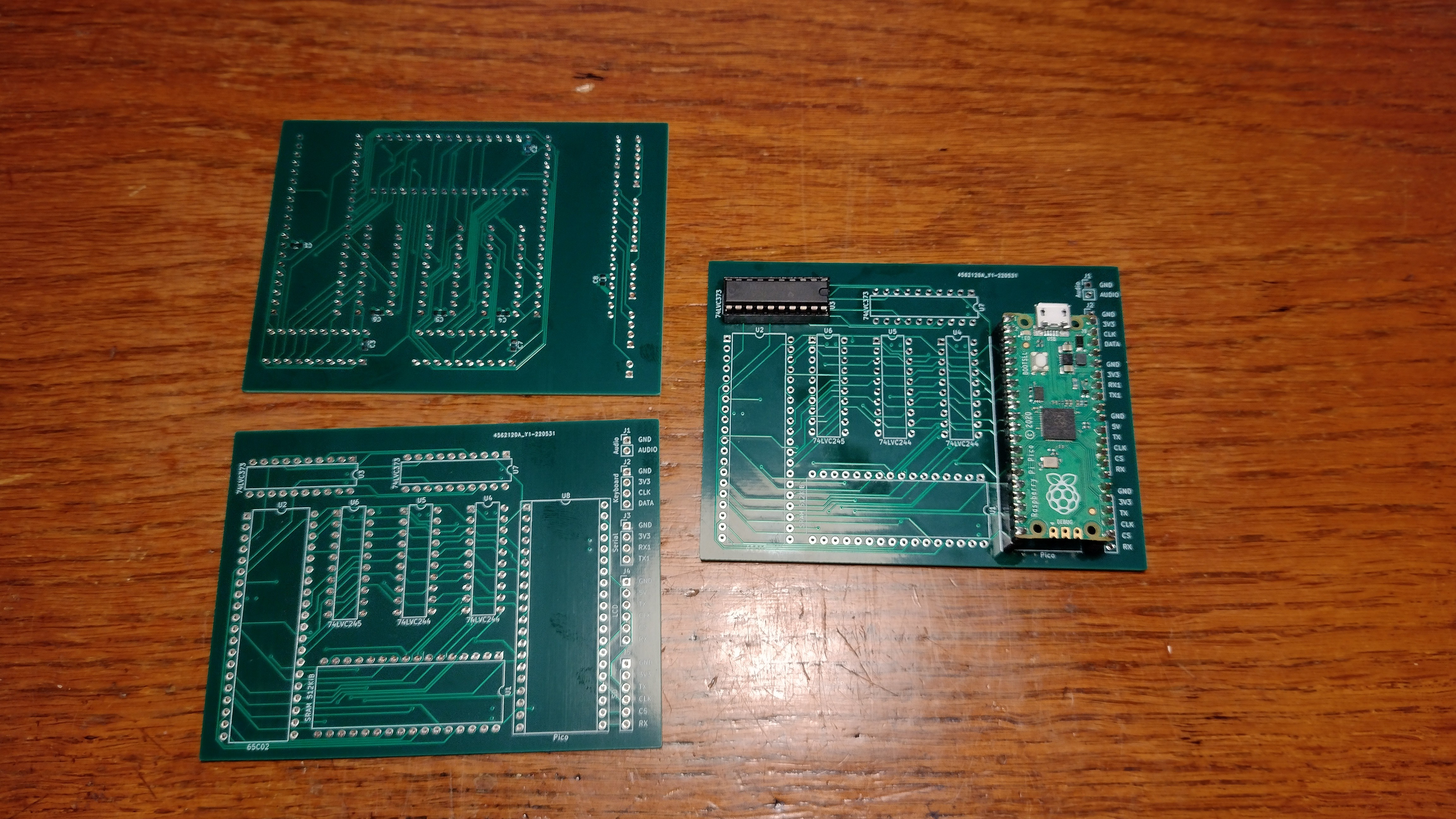

06/17/2022 at 09:26 • 0 commentsI got the PCBs from China yesterday! 5 pcs, 75x100 mm, 4 layer. They are REALLY nice and professional looking, a far cry from the double-sided stuff I did in the kitchen 25 years ago :)

So far everything seems correct. Power supply lines are correct and the first 74LVC373 buffer works correctly. More soldering to be done and a lot more test-SW to write.

![]()

PCBs front, back and partly soldered

PZ1 6502 laptop

I am building a laptop with a W65C02, lots of memory, SID-sound, decent graphics and a filesystem.