Kronos is 3-stage pipelined in-order RISC-V core. The RISC-V ISA is well suited to be implemented as a classic pipelined risc architecture, and this core is no exception. An overview of the Kronos core is illustrated below, visualizing the three stages. The core is fine tuned for single-cycle execution. A deep dive into the core can be read here.

When I had first completed the core, I wanted to quickly check it out in action. The iCEBreaker FPGA board (housing the Lattice iCE40UP5K - 5280 LUT) I had on hand came packaged with the 7-segment display PMOD. So, I strapped the core onto a simple bus to interface with it. This led to the Snowlfake "SoC", and here you can see here, it finding prime numbers - Source.

Now that I knew the core was viable, I designed the project flagship - KRZ (Kronos: Zero Degree), a SoC on the iCEBreaker to showcase the Kronos core.

- 128KB of RAM as 2 contiguous banks of 64KB.

- 1KB Bootrom for loading program from flash to RAM, and general purpose registers for warmboot.

- Configurable UART TX with 128B buffer.

- Configurable SPI Master with 256B RX/TX buffers. Max 12MHz.

- 12 Bidirectional configurable GPIO, with debounced inputs.

There's a neat trick here. The bootrom, and two 64KB banks of main memory are individually arbitrated. The Kronos Instruction Bus and Data Bus can access different parts of the memory simultaneously without halting each other. They can access the entire memory, and only need to be arbitrated if they are accessing the same section. But, usually, most of the code should be run from bank0, while frequent data like the stack will be in bank1. In a design without cache, this setup will lead to optimal performance.

This is one of the reasons why Kronos on KRZ SoC strikes a decent 0.7105 DMIPS/MHZ (risc-v testing). The Kronos core is feature complete, and is officially listed on the riscv-cores-list.

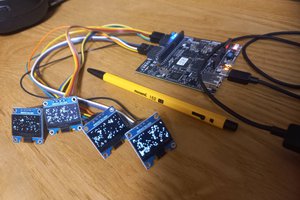

But! The real reason why I built the KRZ was to have it run a native port of the Arduboy! A core can only shine when it runs awesome software.

When I first saw the Arduboy bootlogo scroll down the OLED, I was like "#$#$ #$## this works!!!". This is the krzboy project, and is a work-in-progress (more exciting details to follow soon). However, I did rush for a nice demo of ArduBreakout running smooth.

Real talk, I initially started this project to build some street cred as a digital designer (my trade). The RISC-V ISA and the open-source community that has grown around it is absolutely beautiful, and I want to be a part of it. If it wasn't for the maturity of the riscv-toolchain and the effort the community has put into it, I wouldn't have attempted to build this core. As a bonus, I also get something neat to present during job interviews, instead of just my prosaic grad school work on formal theory.

Sonal Pinto

Sonal Pinto

Dylan

Dylan

Epsilon

Epsilon

Samuel A. Falvo II

Samuel A. Falvo II

Sungwoo

Sungwoo