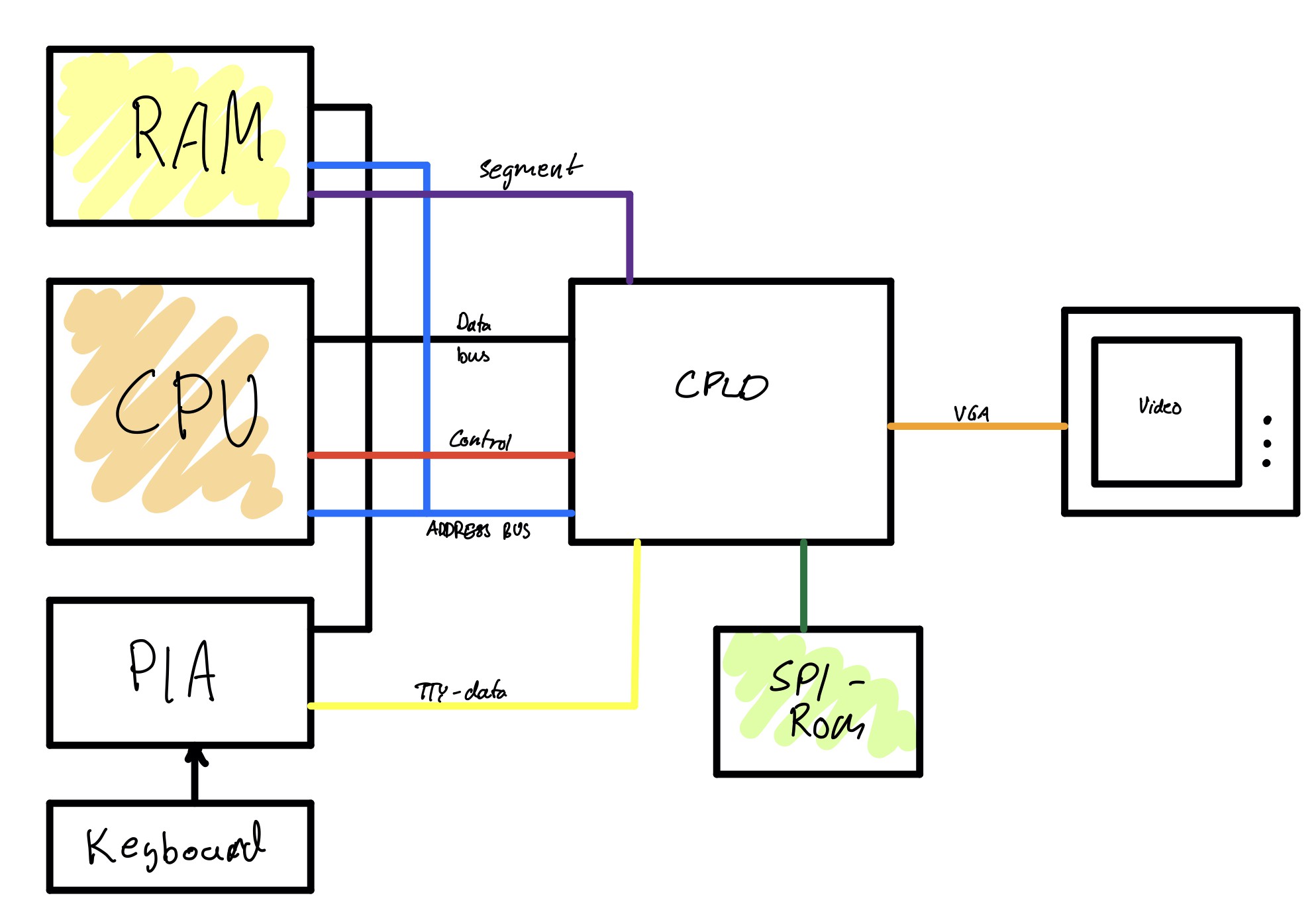

A block diagram of the Melba computer is shown below, and looks pretty similar to the first page of the schematic.

The 6502 CPU executes instructions from the RAM with some minor help in decoding the address from the CPLD. The PIA is used to read the keyboard and write characters to the Video Terminal inside the CPLD.

At first boot, however, the RAM contains random garbage, and no executable code. To make the CPU do useful work; we have to fill the RAM with a Woz-monitor and the Apple Integer BASIC in the correct locations. These has been stored inside a small SPI EEPROM, 25LC640A, and a module in the CPLD sends a read command to the EEPROM and reads the full 8192 bytes, while outputting the RAM address on the address bus and the data on the data bus.

Filling the RAM will have to be done while the CPU is still in reset and the CPU will also have to tri-state its buses. On the Z80, the buses are tri-stated during reset, but the 6502 needs a separate pin for this.

Christian Bjelle

Christian Bjelle

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.