I assembled the circuit boards today, and started some rudimentary performance analysis.

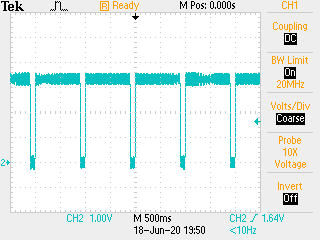

The additive phase noise appears to be negligible, and is actually drowned out by the phase noise from the GPSDO PLL adjustments. The phase noise bandwidth appears to be less than 2 Hz over four seconds, but for longer periods the results become blurred by the GPSDO correction drift.

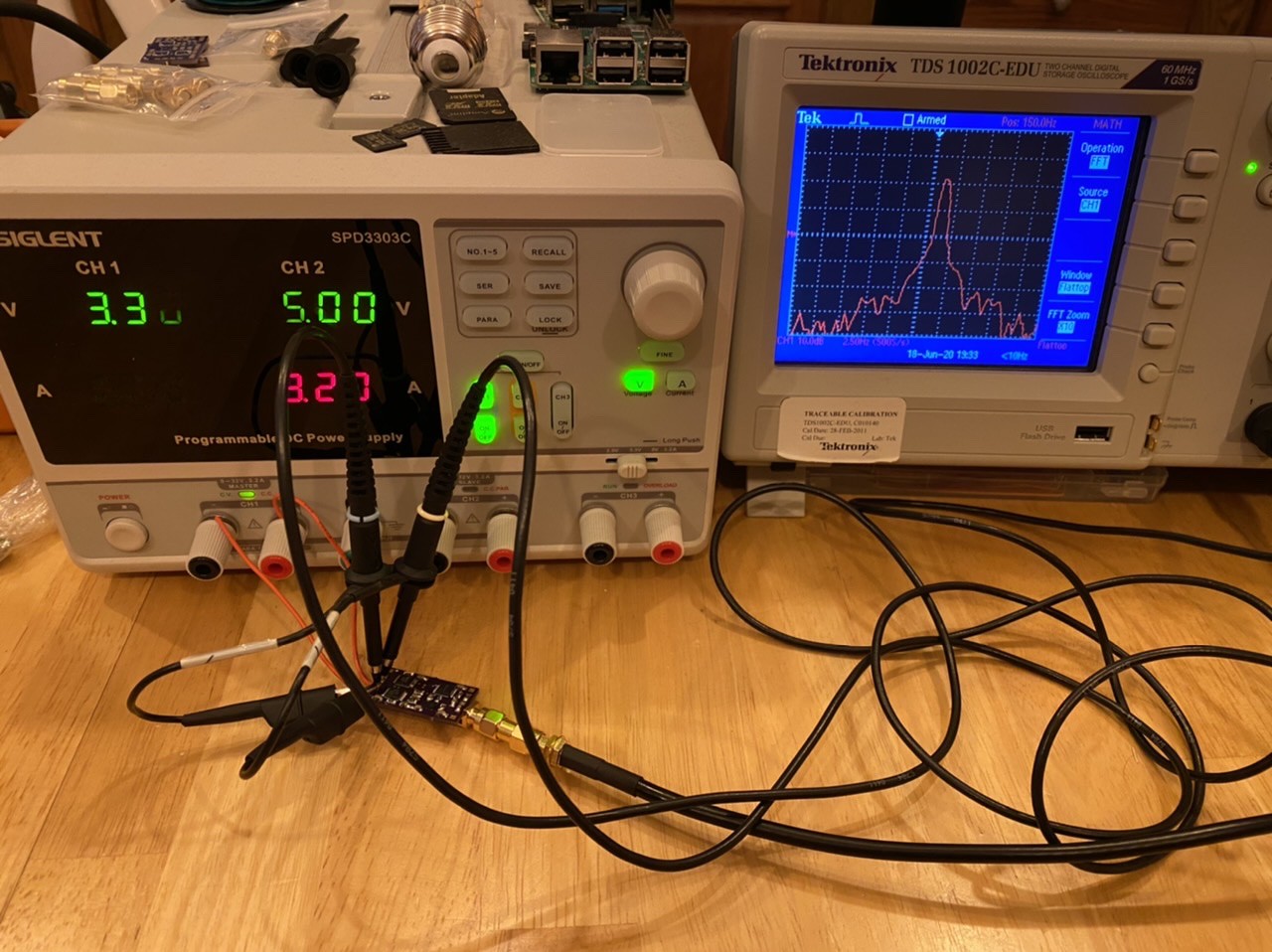

I managed to catch the power supply mid display-scan, but it is set to 3.3V and the board is drawing 60mA. Here's a screenshot from the scope. The internal crystal reference of the scope is offset by about 150Hz which makes it possible to use under-sampling to measure the ultra-fine bandwidth of the clock output. You can see between the two images that the scope crystal frequency has drifted up about 4 Hz.

The polarity detection part of the circuit does not function correctly, so I'll be sending off a board revision to correct it. The PPS duty cycle should be 10% not 90%.

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.