The results are finally available !

[yg@localhost test6_bigLFSR]$ ./test.sh Simple gate version setup (RAM+time) : 290 4260 0:00.00 580 4528 0:00.00 1160 4800 0:00.00 2030 5576 0:00.00 2900 6132 0:00.00 5800 8272 0:00.01 11600 12296 0:00.02 20300 18568 0:00.03 29000 24744 0:00.05 58000 45264 0:00.09 116000 86364 0:00.18 203000 148588 0:00.30 290000 210440 0:00.44 580000 417476 0:00.91 1160000 831120 0:01.77 2030000 1451852 0:03.11 Detailed gate version setup (RAM+time) : 290 5480 0:00.00 580 6652 0:00.01 1160 8668 0:00.01 2030 12052 0:00.03 2900 15336 0:00.04 5800 26764 0:00.08 11600 49428 0:00.16 20300 83392 0:00.28 29000 117340 0:00.39 58000 230732 0:00.79 116000 457372 0:01.53 203000 797488 0:02.70 290000 1137588 0:03.81 580000 2270924 0:07.51 1160000 4538012 0:15.17 2030000 7938396 0:27.71 Benchmark : OK

I wanted to test several things :

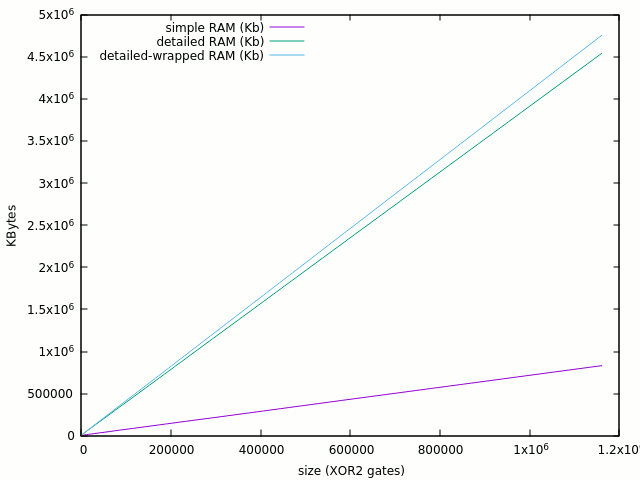

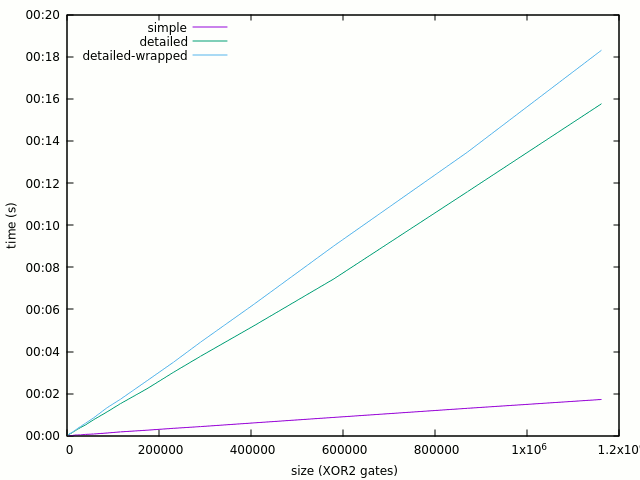

- Time and RAM are roughly linear so it's a good news. Note that this is only the setup performance.

- Setup time is 10× with the detailed version, and I don't even run an iteration !

- The detailed version uses about 6× more RAM, but that amounts to about 4KB for a single gate !

This means that with 16GB RAM, it is possible to simulate approx. 20M gates and analyse 3M gates.

You can run this test manually with the newer archives. It's a stress test for the system and the behaviour will change depending on your computer configuration. I don't assume your CPU speed or RAM size, so run it cautiously.

---------------------------------------

Update 20201121:

I managed to run the design inside the wrapper, and the overhead is marginal (5% size, <10% time)

290 5516 0:00.00 580 6808 0:00.01 1160 9200 0:00.01 2030 12676 0:00.03 2900 16228 0:00.04 5800 28088 0:00.08 11600 51880 0:00.17 20300 87528 0:00.29 29000 123120 0:00.41 58000 241696 0:00.78 116000 479028 0:01.55 203000 835028 0:02.78 290000 1191172 0:03.92 580000 2377824 0:07.98

The graphs will be auto-generated if you have installed gnuplot on your system.

I still have to perform dynamic comparisons and I have not even started re-implementing the gates probes.

Anyway the 10x speed&size gain with the "simple" version vindicates the choice and efforts to make 2 versions.

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.