So far, so good...

Hello, Hackaday! I want to tell you about my pet project aimed at creation of homebrew computer. I've been doing this project for three years. In this entry I want to briefly summarize what's been done.

Why I'am doing this?

Mostly for fun, of course. For 20+ year I've been doing software development and I know a lot about it. But the hardware has always remained a mystery for me. To fill in that gap in my knowledge I made some hardware projects (including making my own CPU in FPGA, but that's out of scope). Another reason is retrocomputer nostalgia. Combine that together and you get main idea of this project - create retro-styled computer system with hardware and software.

Why MC68008?

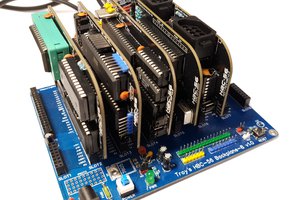

Initially I wanted to use Intel 8080, Z80 or Intel 8086 for my project. But I really do not like it's instruction set and segmentation approach (in case of 8086), so I started looking for alternative. Motorola 68000 series immediately catched my eye for it's clean and lean pdp-ish instruction set. Personally, I think that it is a shame that x86 architecture took over the world. It should be 68000. To reduce complexity I've chosen 8-bit bus version of that CPU - MC68008. I was able to get 8MHz rated 48-pin DIP chips.

Overall design approach

Speaking of architecture my system is pretty much classical one with CPU, ROM and RAM using one system bus. There are four expansion slots which are buffered by 74245 buffers and provide expansion capabilities for system. Glue logic and address decoding are implemented using ATF16V8 and GAL22V10D PLD chips.

One interesting feature of my system is usage of Atgema640 MCU as main peripheral controller. It allows me to save a lot of work by providing single-chip solution for several system functions:

- UART

- SPI bridge for SD card access.

- PS/2 keyboard controller

- Programmable interrupt controller

- (planned, but not implemeted):

- EEPROM controller

- Real-time clock

By wiring a lot of peripherals through MCU chip I translate a lot of design issues from hardware to firmware, which greatly reduces time and effort required to integrate them into system. But this approach has one major drawback as MCU chip is quite slow. For example when performing SD card IO main bottle neck is not SPI or memory interface, but internal operations inside microcontroller program (bits and ports manipulation). This is a tradeoff of the design decision - you get simplicity by sacrificing performance.

Software ecosystem

For my computer I've written my own operating system which provides basic services for applications: filesystem, program loading and running, standard user IO using UART, keyboard and monitor controller. I also designed small set of basic system utilities (like, "ls", "mkdir") and applications (editor, toy lisp interpreter, ported PicoC interpreter). I've used some of 3rd party code to save time and effort, full list is provided at gitlab project page.

For software development I use prebuilt GCC cross-compiler for M68K architecture. In future I plan to port some c compiler and thus provide onboard system development capabilities.

Matt Stock

Matt Stock

Samuel A. Falvo II

Samuel A. Falvo II

Troy Schrapel

Troy Schrapel

Stuart

Stuart

It would be interesting to see a block diagram or a schematic of the design.