Hardware

For now I'm mostly focused on AscetiCore, 16-bit CPU core with user/supervisor modes, memory protection, and paging. AscetiCore in a nutshell:

- 16 16-bit common purpose registers (including instruction pointer) used for memory addressing as well as storing operations' results. Special registers accessed by special instructions,

- byte-addressable memory,

- memory-mapped I/O devices,

- MMU operates on 4Kbyte pages,

- context defined as a set of CPU and MMU registers,

- switchable contexts either built in or banked in RAM,

- supervisor context used only for handling interrupts and exceptions,

- no privileged instructions or registers, still meets Popek-Goldberg criterion,

- base instruction set can be boiled down to 27 mnemonics.

AscetiCore ISA is planned to be somewhat extensible, with the basic level fully supporting all the aforementioned features. Extensions will include:

- atomic operation,

- integer multiplication and division with target extension.

I'm planning to cheapskate on FPU by using 68881 or 68882 as an external device.

Here is the current specification of AscetiCore (WIP).

Software

From the software standpoint, my plan is:

- Create a backend for one of modern retargetable compilers.

- Write any missing components of a cross-compiling toolchain.

- Port some OS using that toolchain.

By now I'm only planning my dive into that stuff. My current preferences are:

Tools

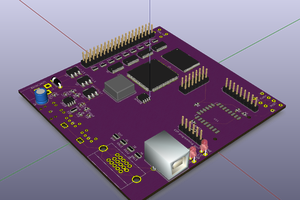

I use nmigen for describing hardware.

I

have a Terasic DE0-Nano prototyping board with Cyclone

IV series FPGA chip. I’m trying not to

rely on any specific feature

of this board or chip so that my design

could be reproduced on any other reasonably specced FPGA platform

with just minor

modifications.

Jock Tanner

Jock Tanner

london almida

london almida

Michael A. Morris

Michael A. Morris

Erik Piehl

Erik Piehl

Alexios C

Alexios C