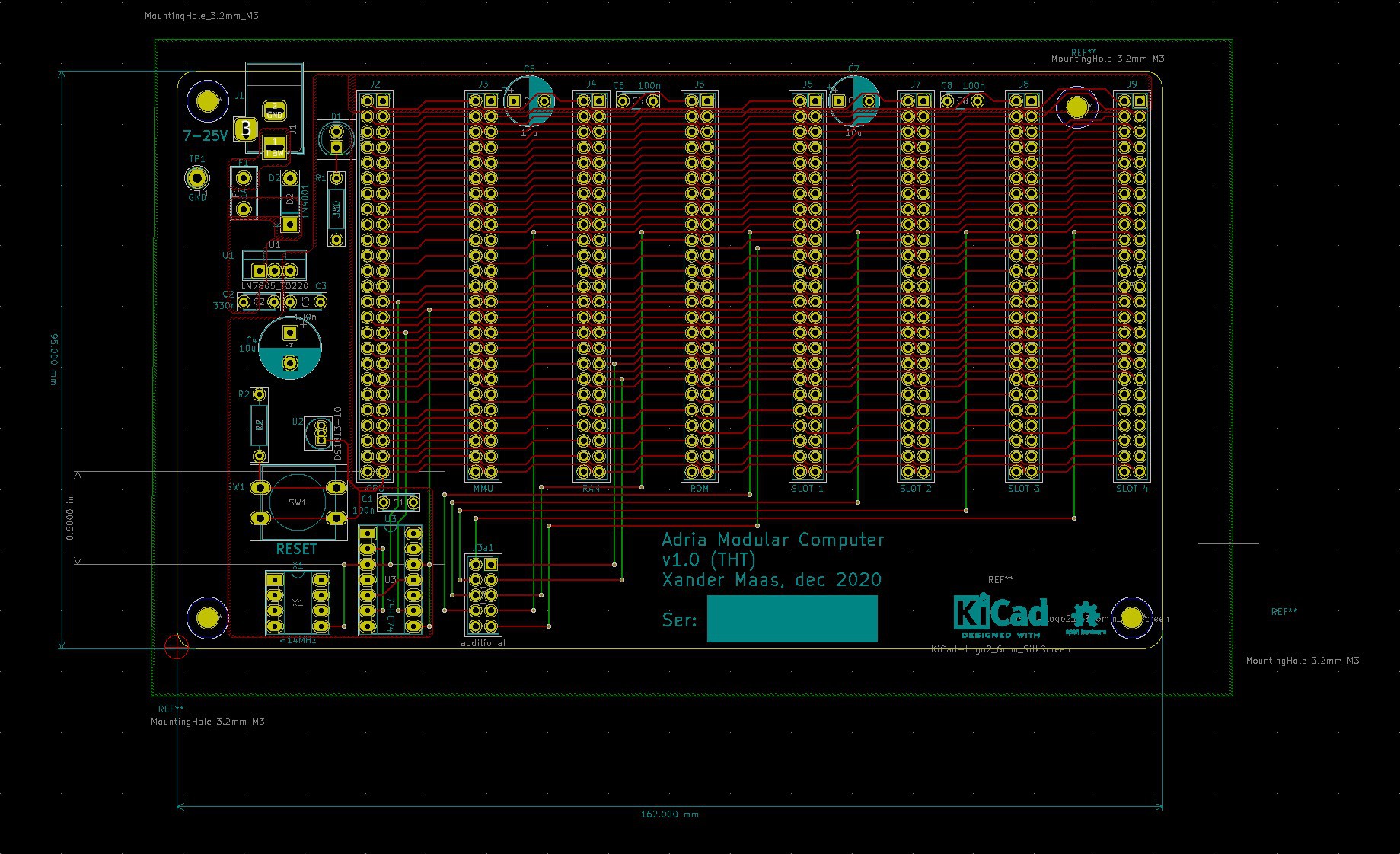

Dimensions

| Backplane | 162mm x 95mm |

| Peripheral boards | 95mm x 50 mm |

Blank templates for the boards (in KiCad format) are available. These should be installed in the KiCad template directory (for your system)

Memory Decoding Logic

Memory decoding is done with two GALs (22V10, I used Atmel). This is the only "slot" with an additional 10-pin connector, which holds the /IOSEL signals and the /DEVSEL signal.

The equations are written for and compiled with PALASM.

/DEVSEL is not used (yet), but theoretical I can use this for selecting an on-card ROM?

Memory Map

The system was designed with a simple memory map. This is the momery map as it is right now. This might change (some compacting is needed)

$FFFF

$FFF0 |________Emulation mode interrupt vectors

$FFE0 |________Native mode interrupt vectors

$FD00 |________Reset routine(s)

$FCA0 |________Fixed jump table

$FC00 |________Interrupt Service Routine(s)

$D800 |________Supermon816 (adapted from original by BigDumbDinosaur)

$D000 |________Intel Hex Uploader (adapted from original by Ross Archer)

$CD00 |________UART driver (inspired by and based on code by BigDumbDinosaur)

#C020 |________UART I/O registers (mapped to UART card using GAL)

$C000 |________

$BFFF |

|

$8000 |________Free RAM

$7FFF |________Supermon816 stack

| (growing down...)

|

|

|

$2200 |________Free RAM

$21FF |

|

$2180 |________UART Channel B TxD buffer

$217F |

|

$2100 |________UART Channel B RxD buffer

$20FF |

|

$2080 |________UART Channel A TxD buffer

$207F |

|

$2000 |________UART Channel A RxD buffer

$1FFF |

|

$02E6 |________Free RAM

$02E4 |________Character scan routine vector

$02E2 |________Character input routine vector

| (Reserved)

$02DE |________Software BRK vector

$02DC |________Software BRK vector checksum

$02DA |________Software INT/IRQ vector

$02D8 |________Software INT/IRQ vector checksum

$02D6 |________Software NMI vector

$02D4 |________Software NMI vector checksum

$02D2 |________Software Reset vector checksum

$02D0 |________Software Reset vector

$02EF |

$0266 |________Free RAM

$0265 |

|

$0246 |________(Supermon 816 auxbuffer)

$0245 |

|

$0200 |________Keyboard buffer

$01FF |

|

$0100 |________Hardware stack

$00FF |

|

$0000 |________Zero Page

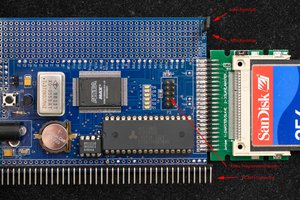

RAM

The board currently available is for an AS6C1008 SRAM. This should give the computer 128 kbyte of RAM

ROM

Two boards are designed,

- A board for the 28C256 (32k x 8) variants EEPROM, currently only 16 kbyte is used.

- A board for the 29F040 4 Mbit Flash (this has worked well in my previous design, Lilith)

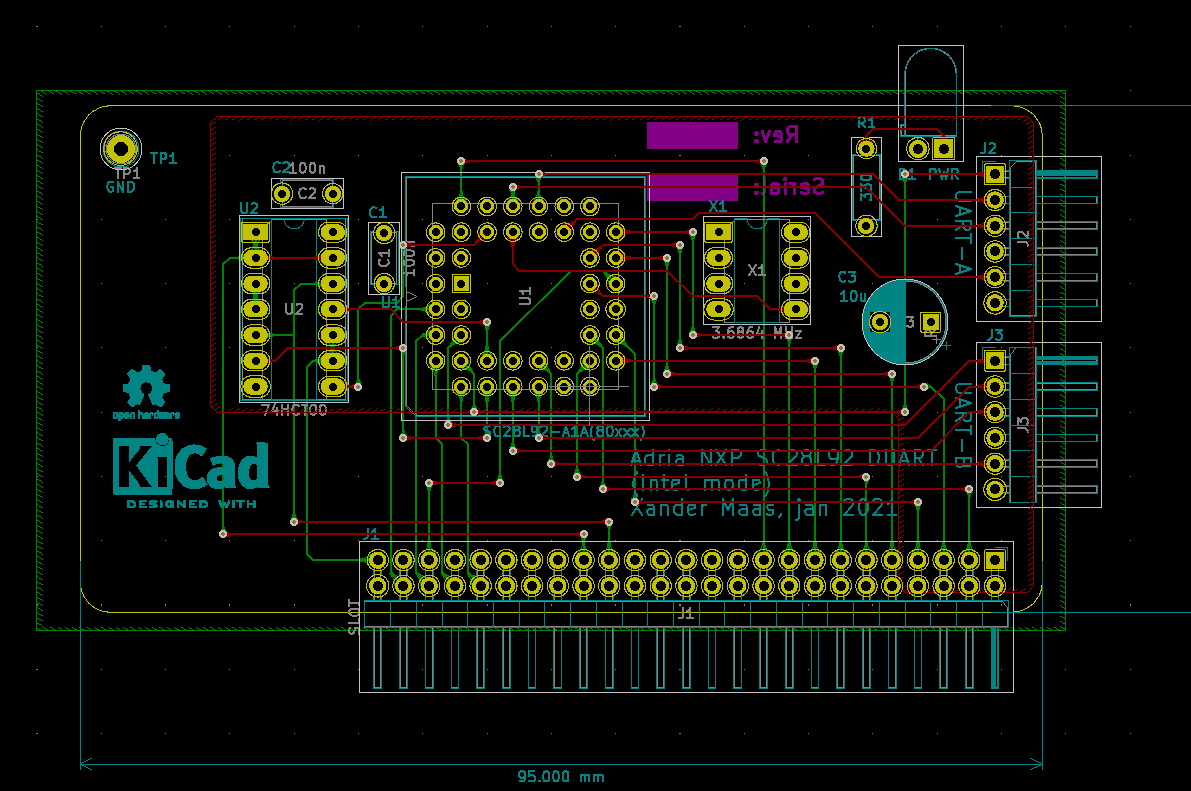

UART

There are currently two options for UART:

- A 6551 based board (not the WDC 65C51, because of hardware issue)

- A NXP SC28L92 based board (has 2 UARTs, supports higher speeds)

Xander Maas

Xander Maas

SHAOS

SHAOS

Plasmode

Plasmode

gbm

gbm

Koen van Vliet

Koen van Vliet