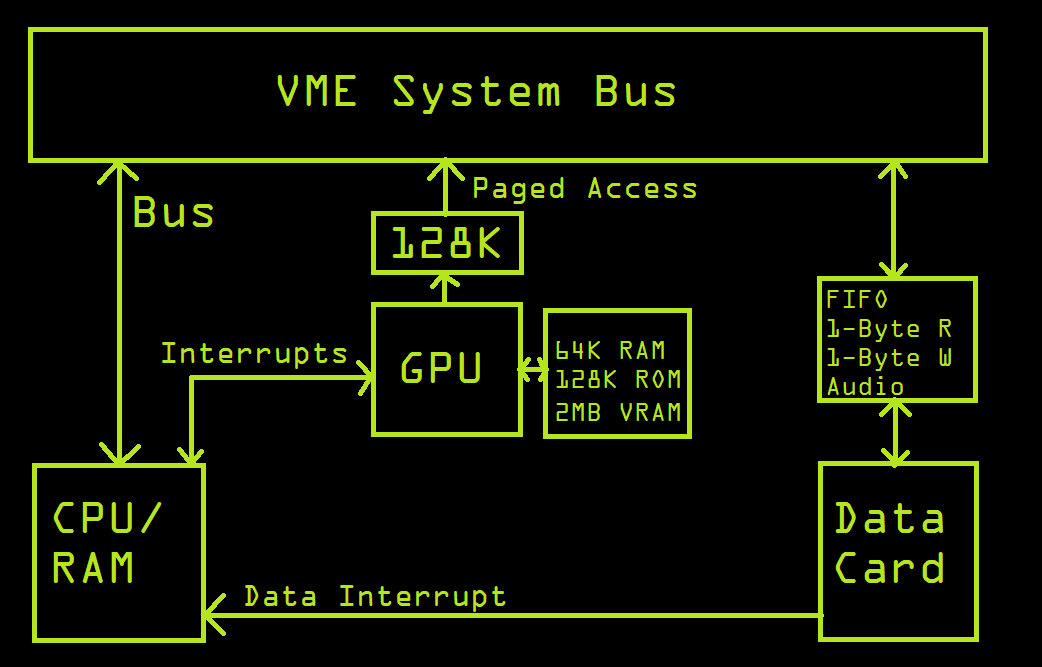

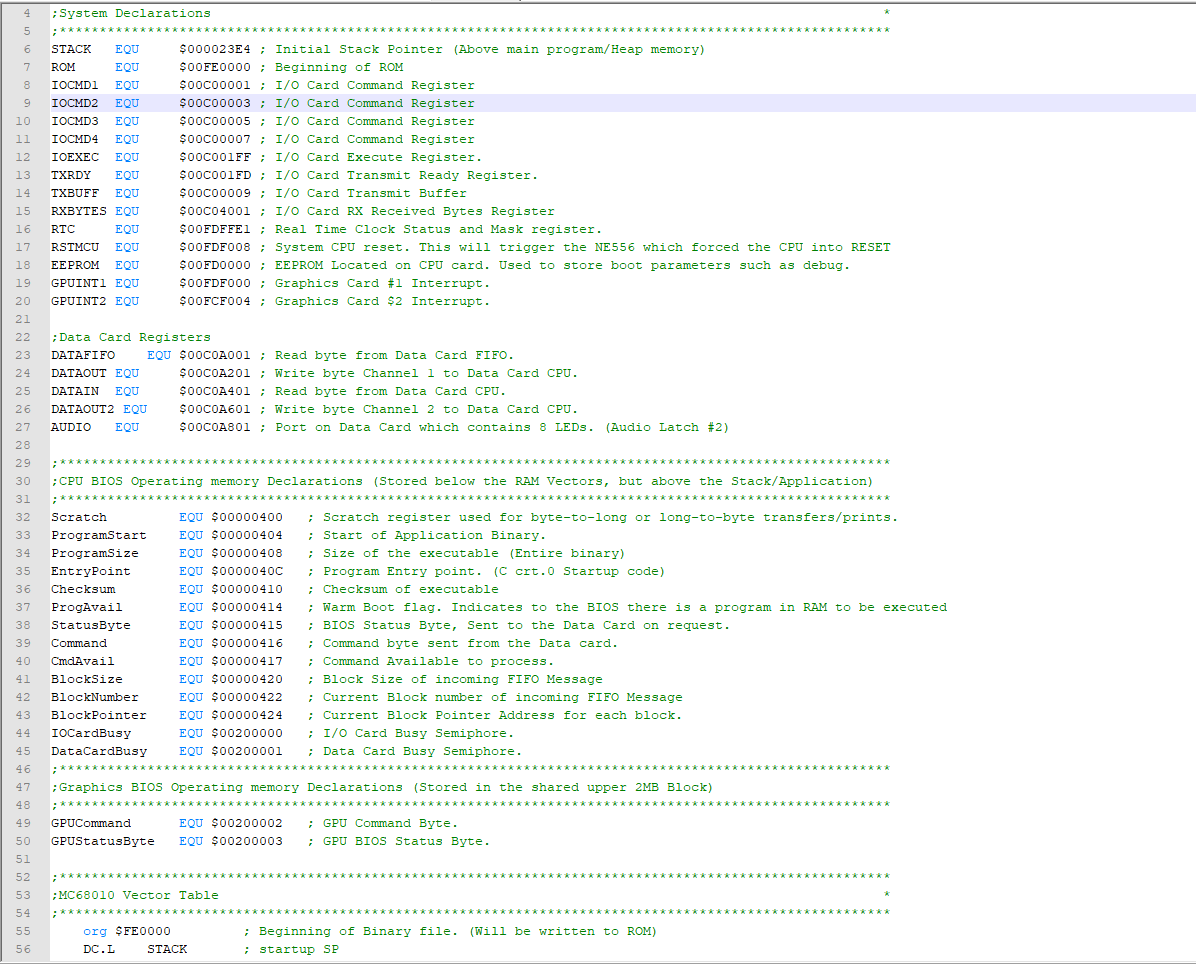

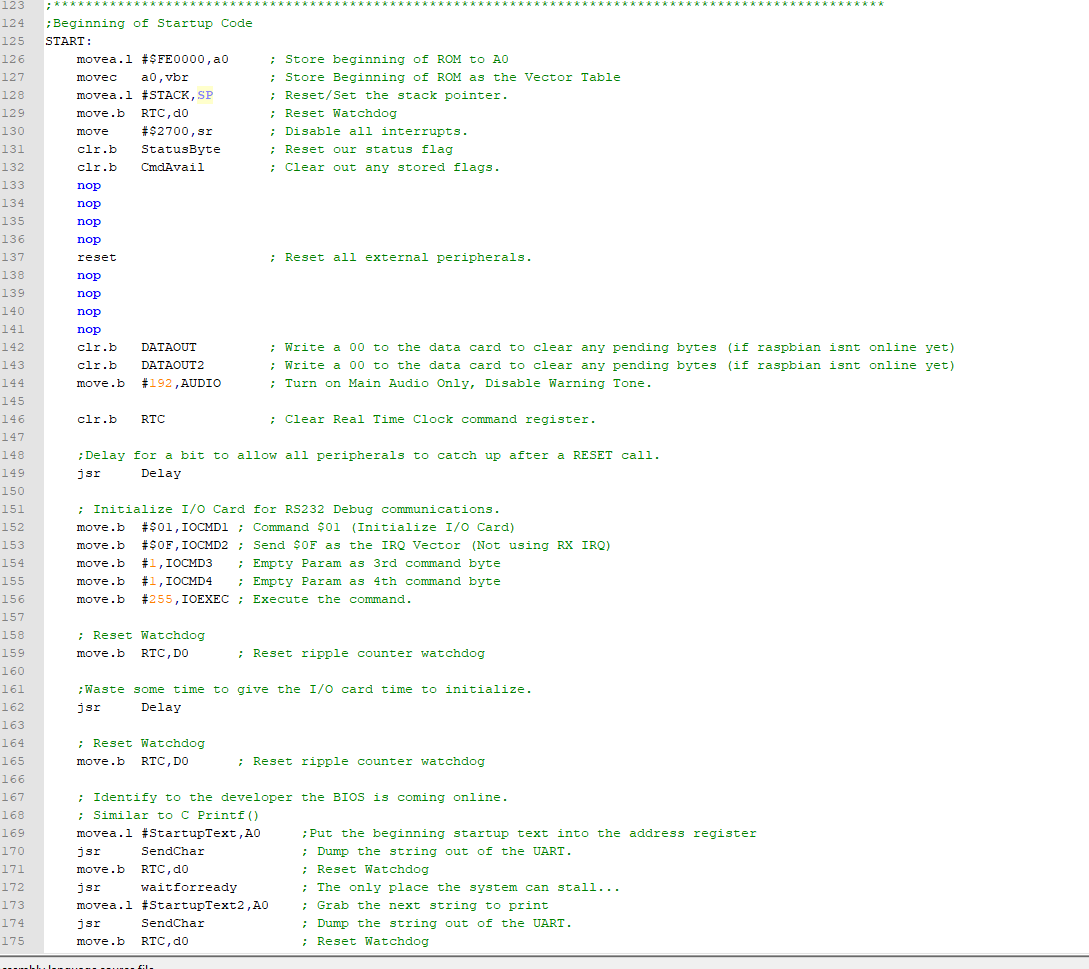

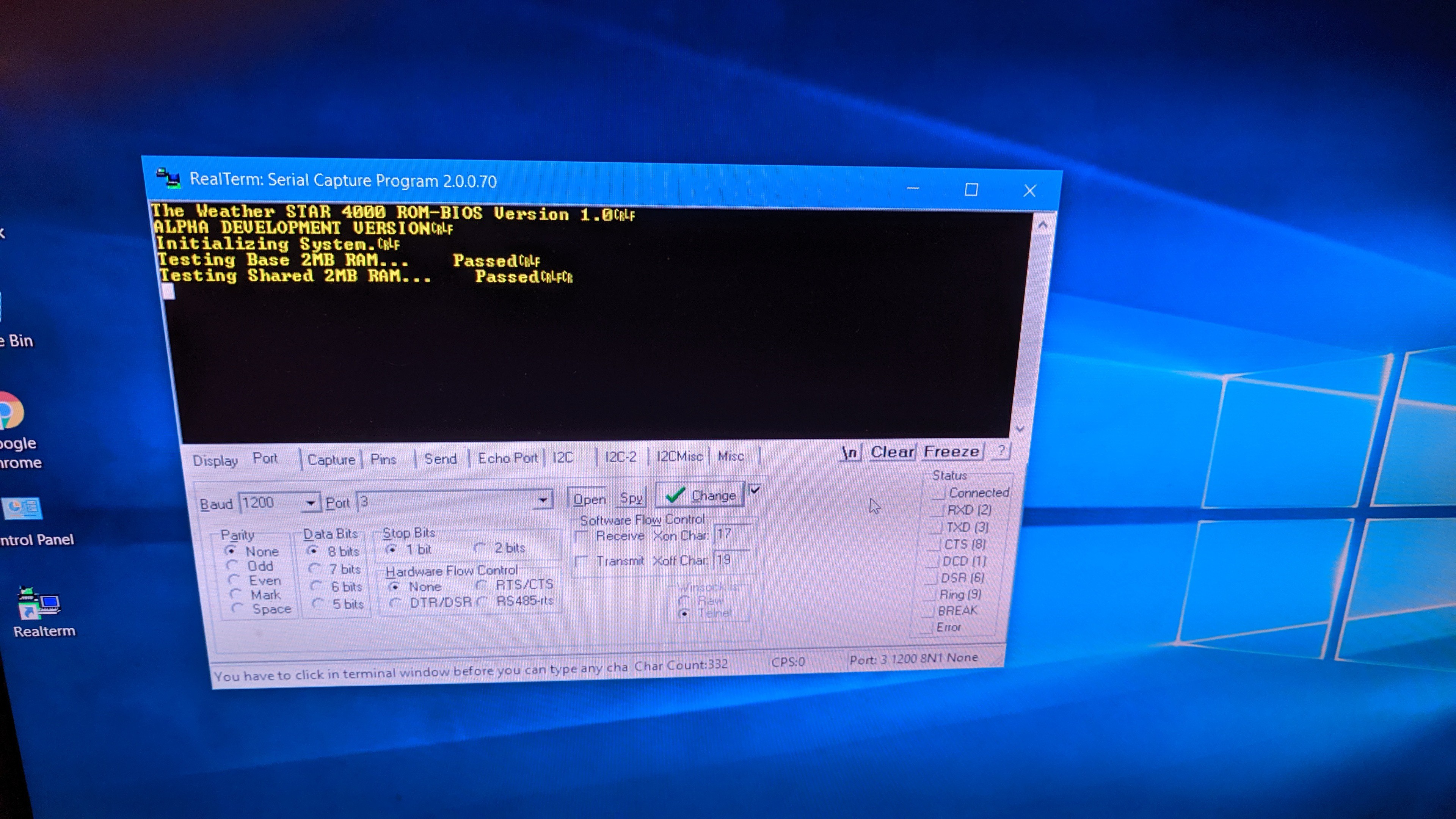

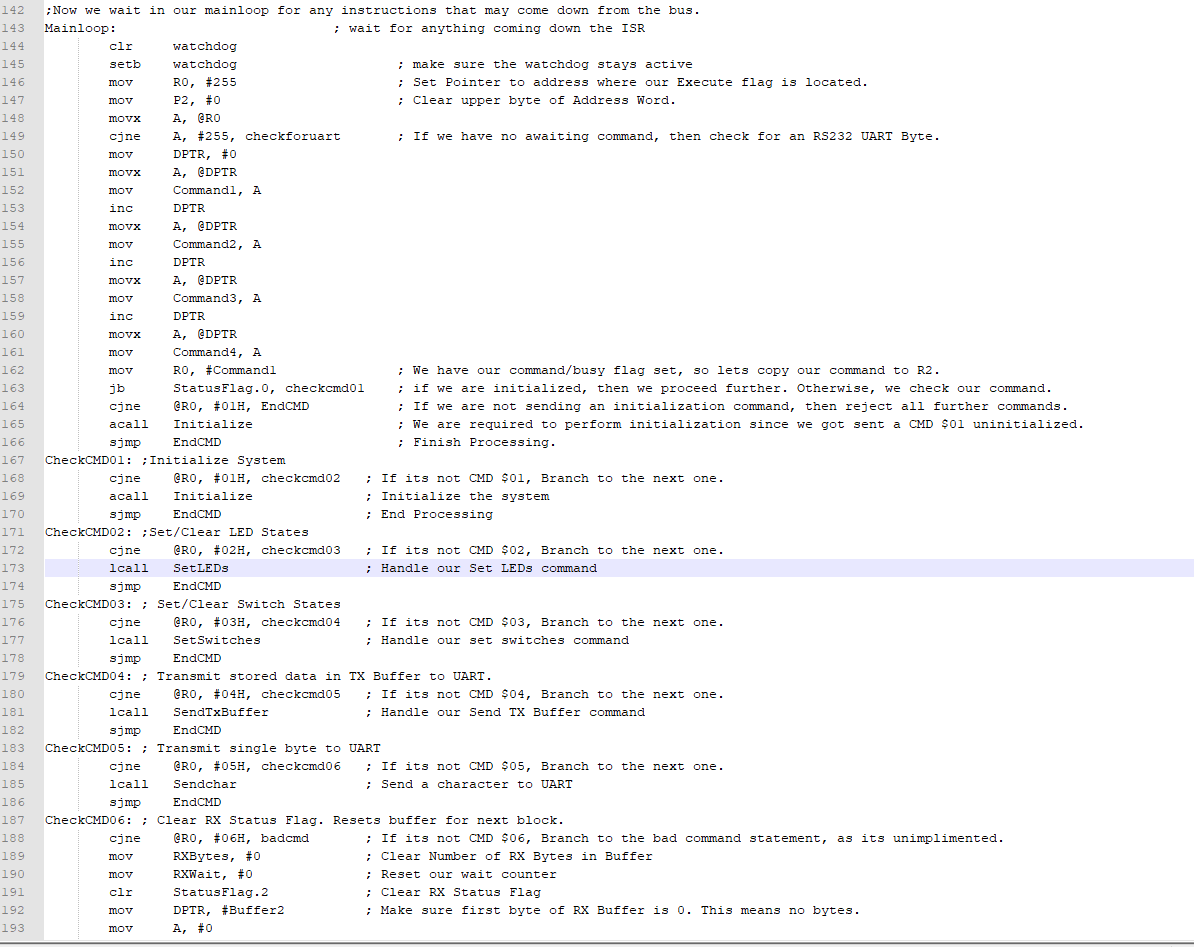

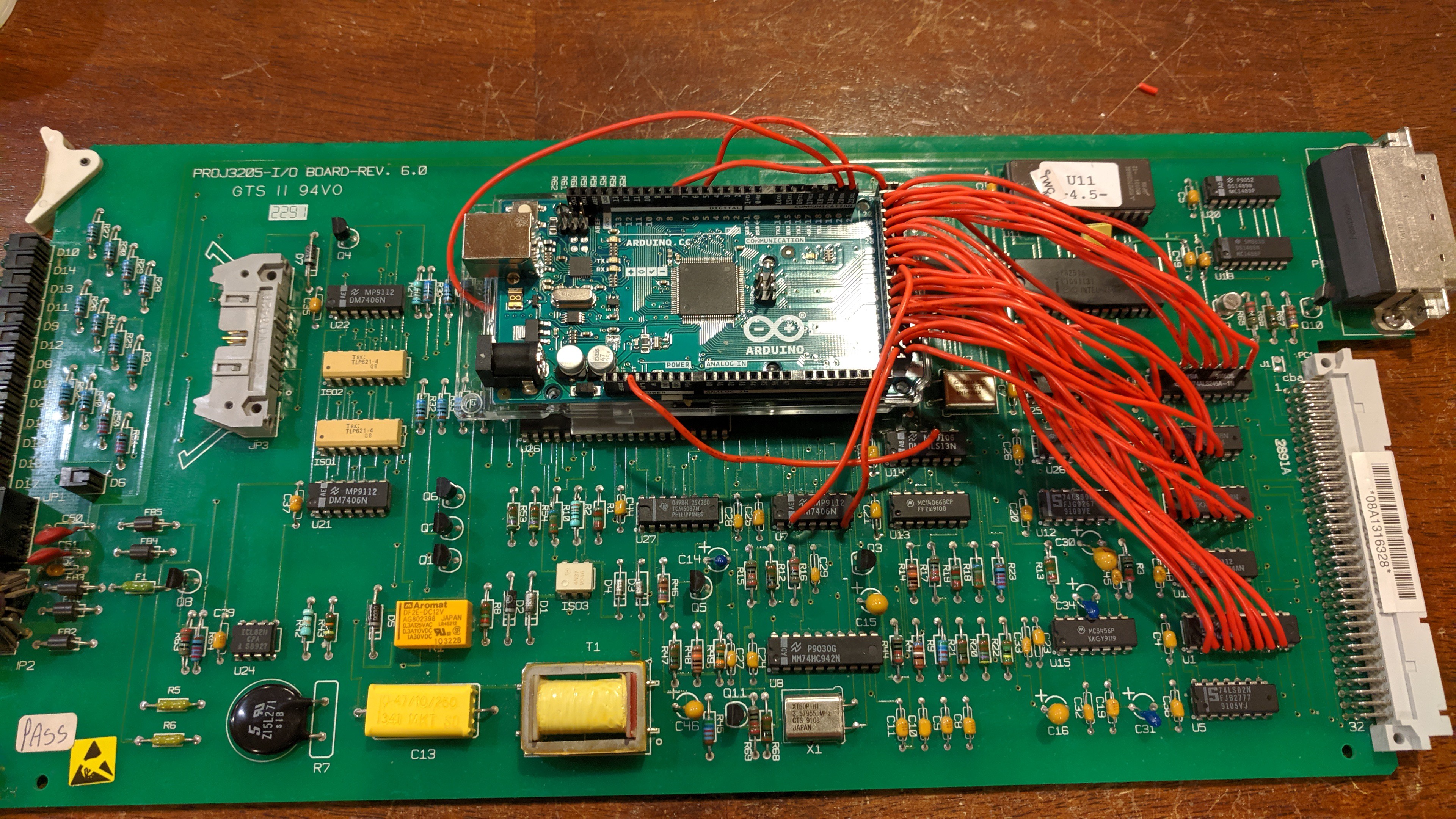

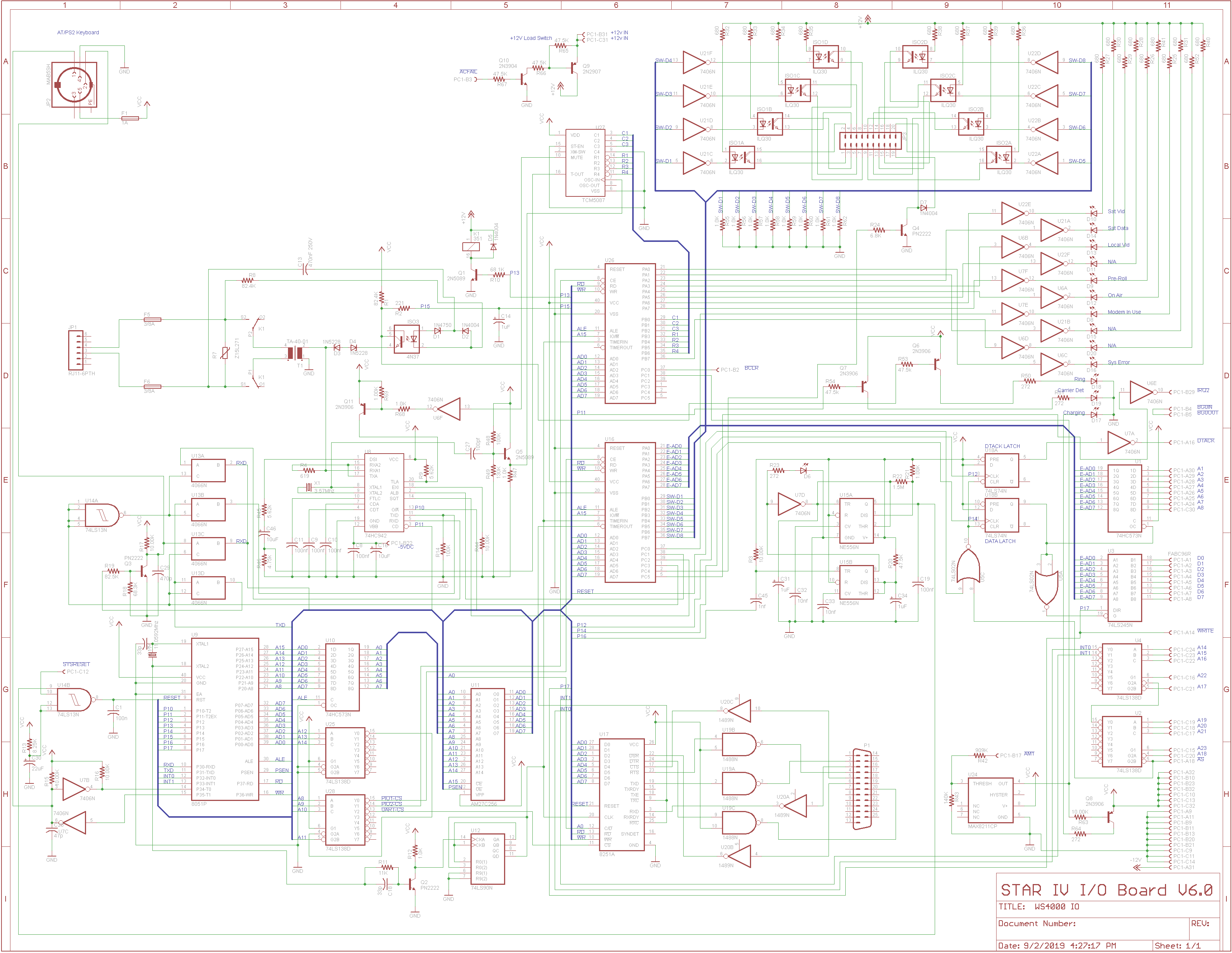

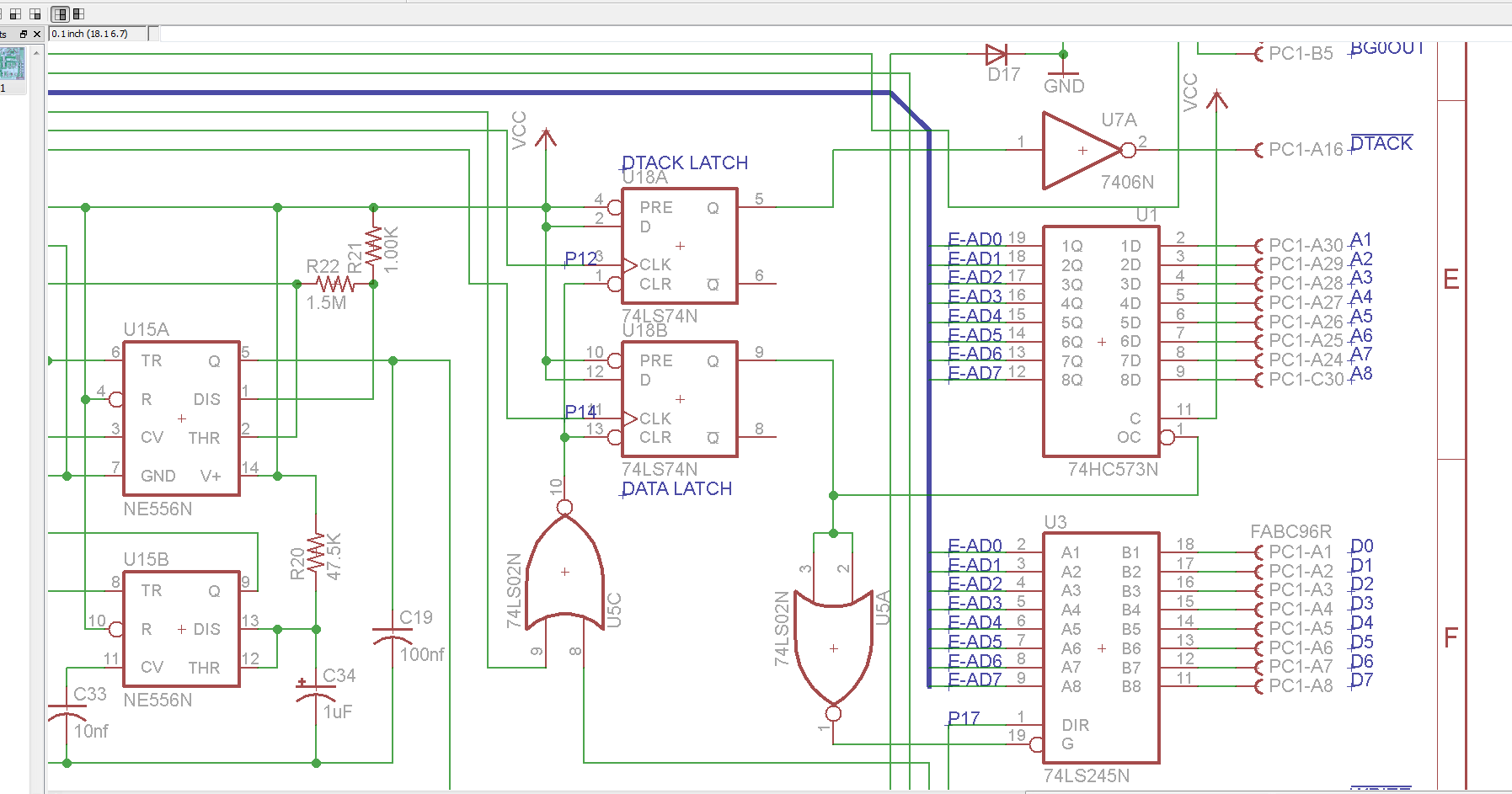

We bring this 1980s machine into the modern world as an IoT device to receive data and render presentations like it used to, once again... Bridging the digital divide between 68K satellite-era hardware and the internet :-)

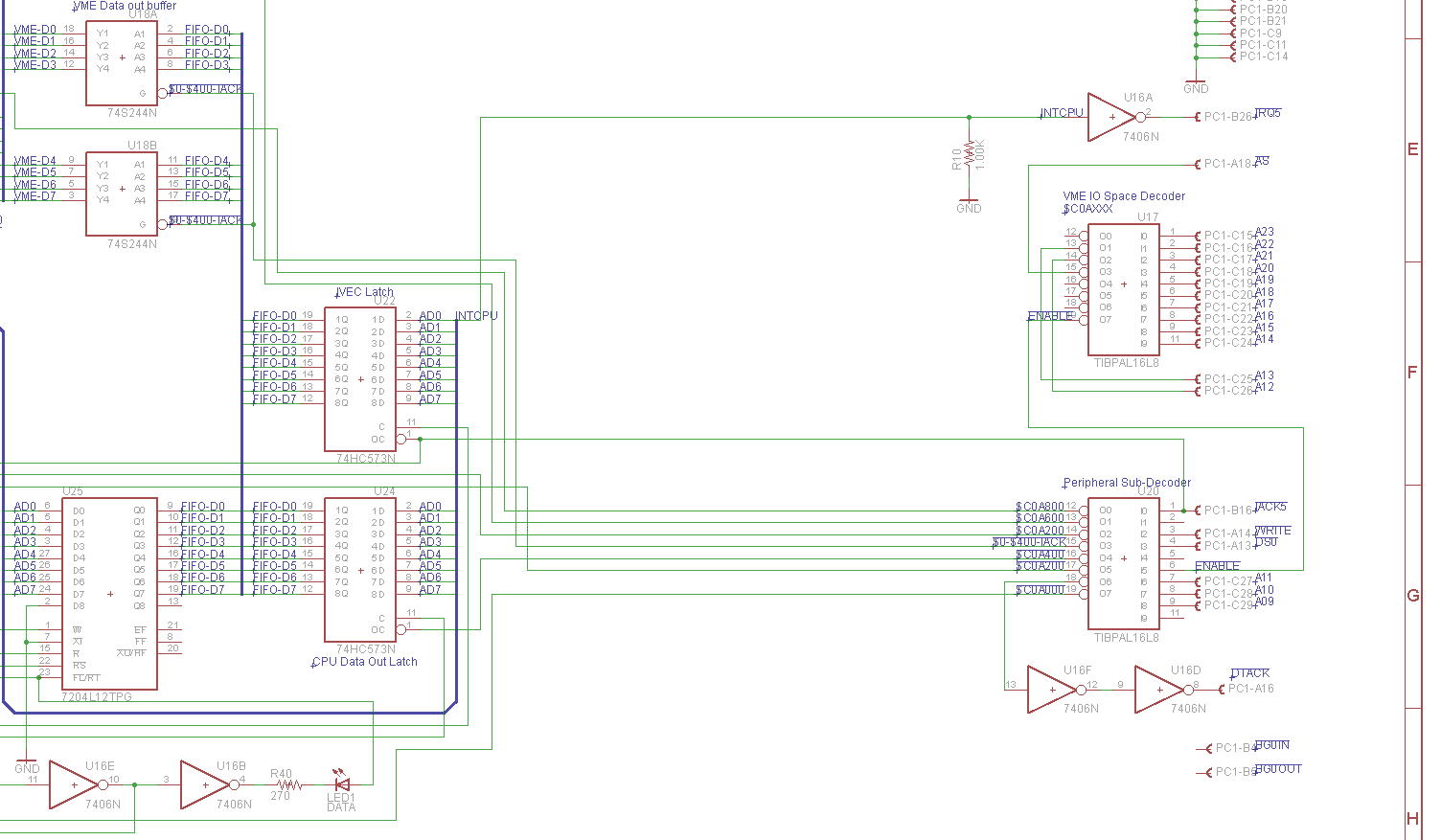

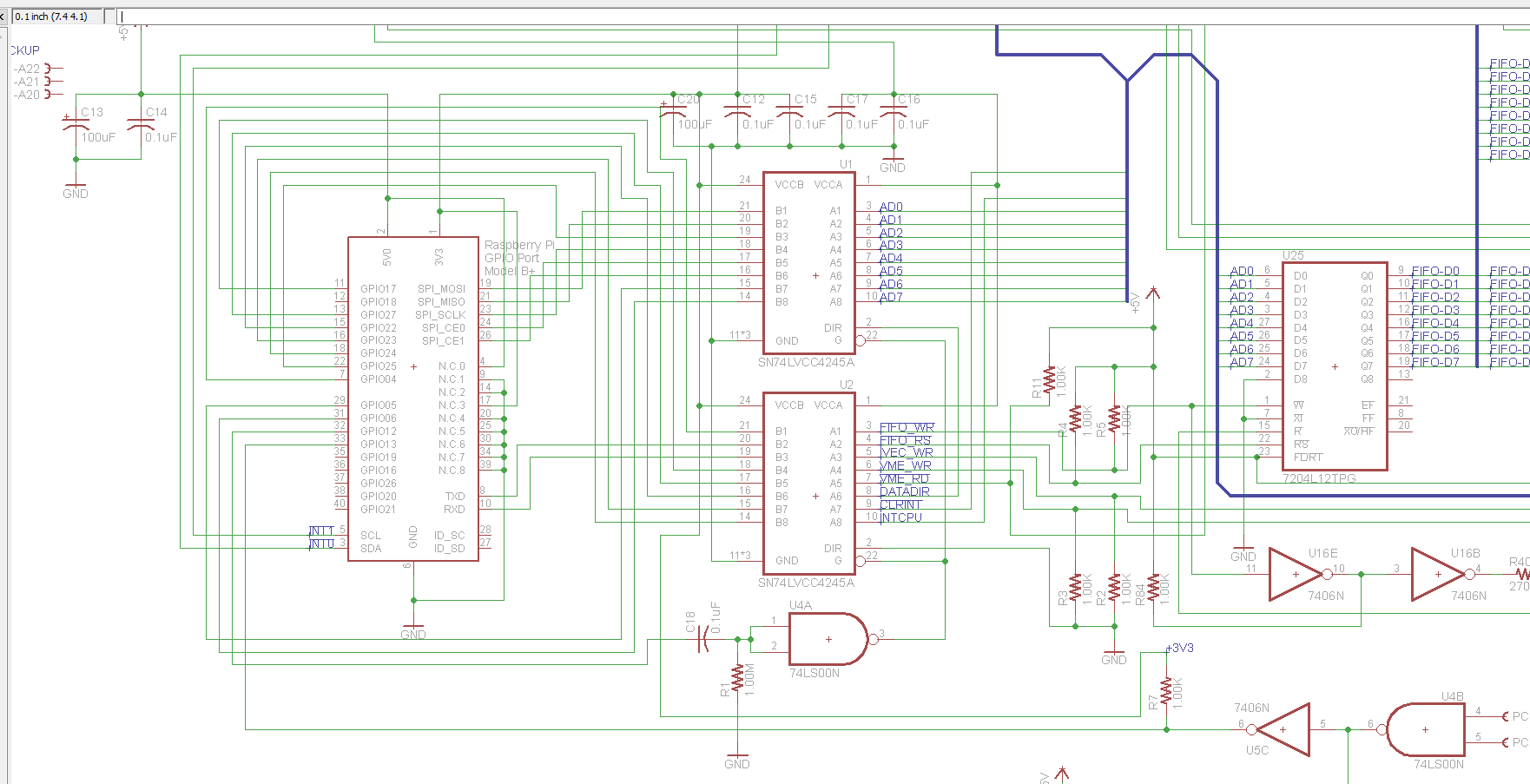

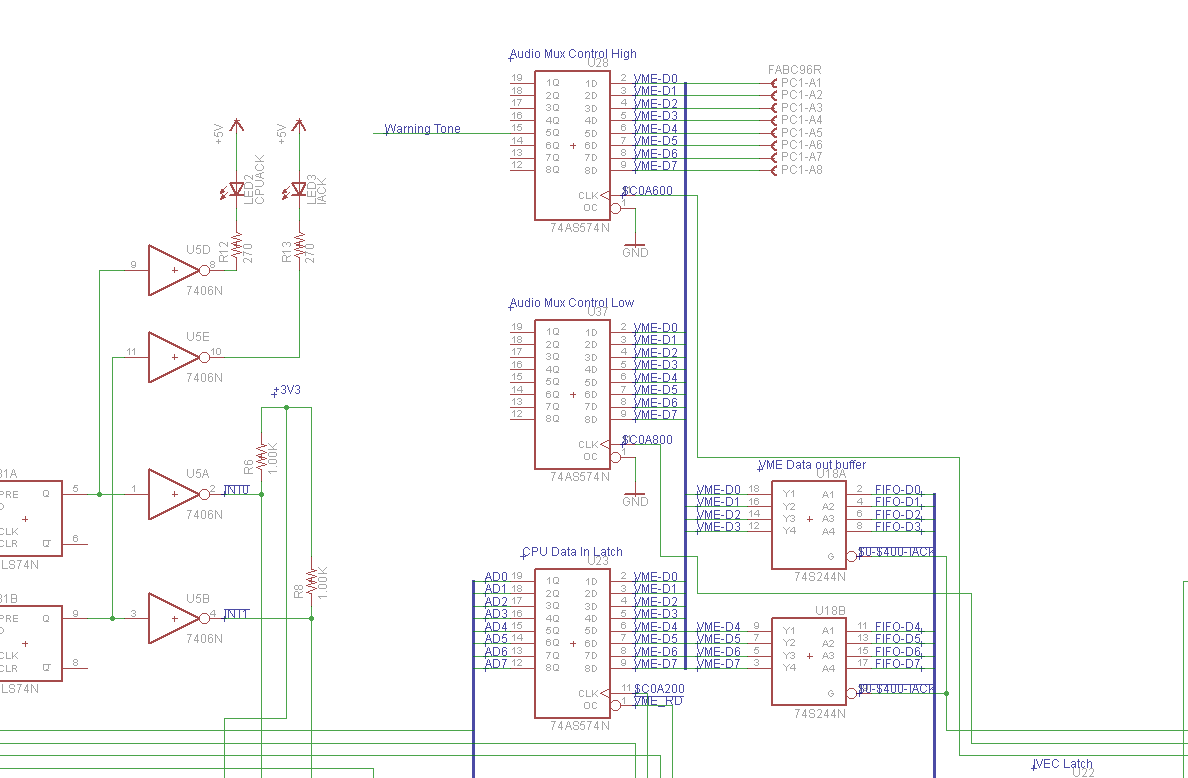

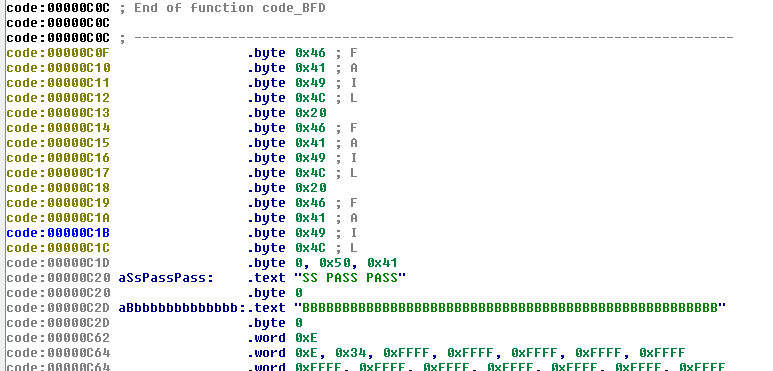

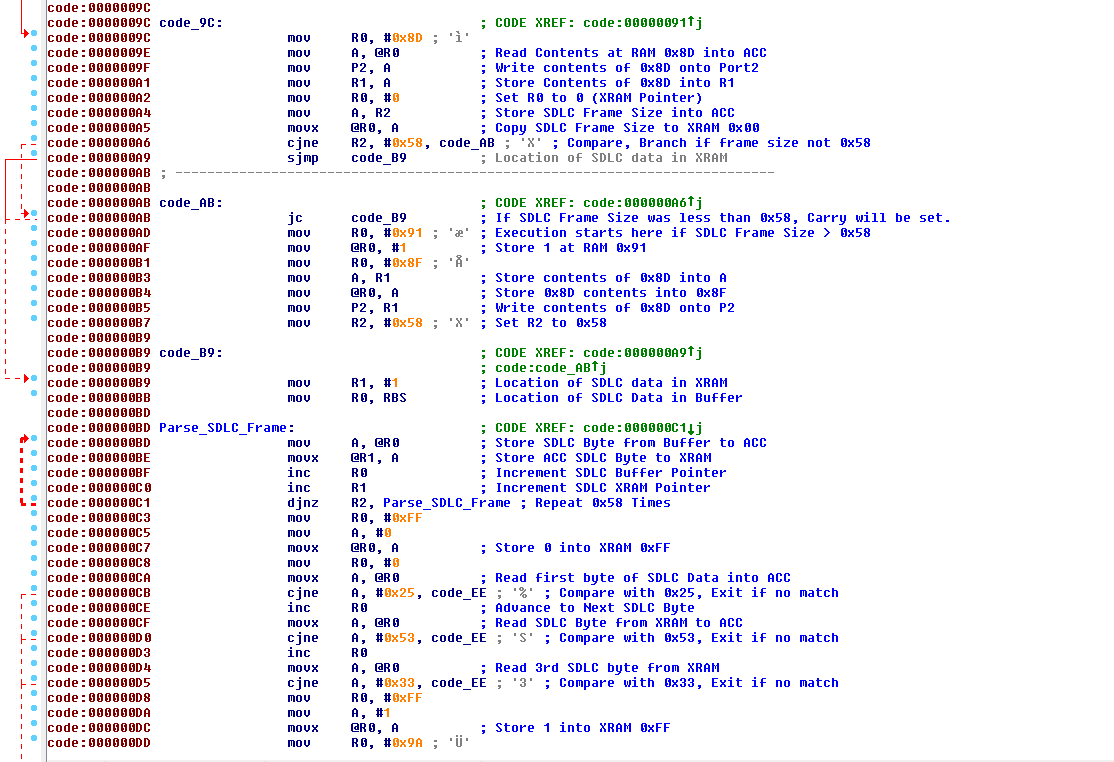

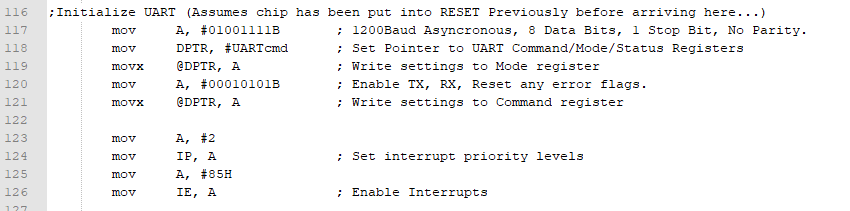

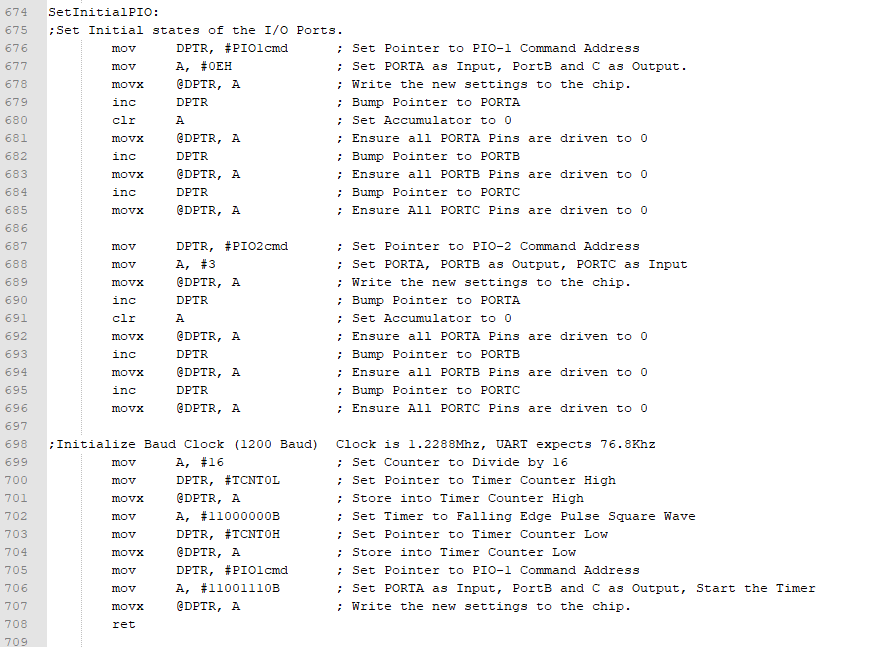

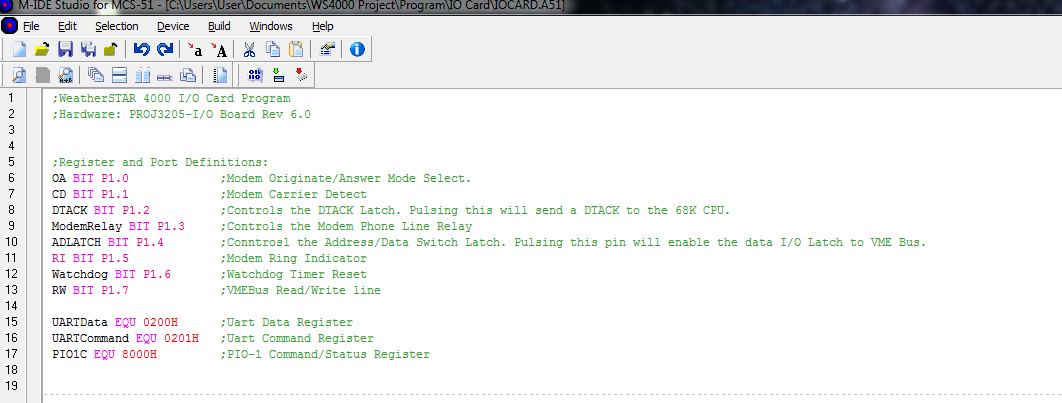

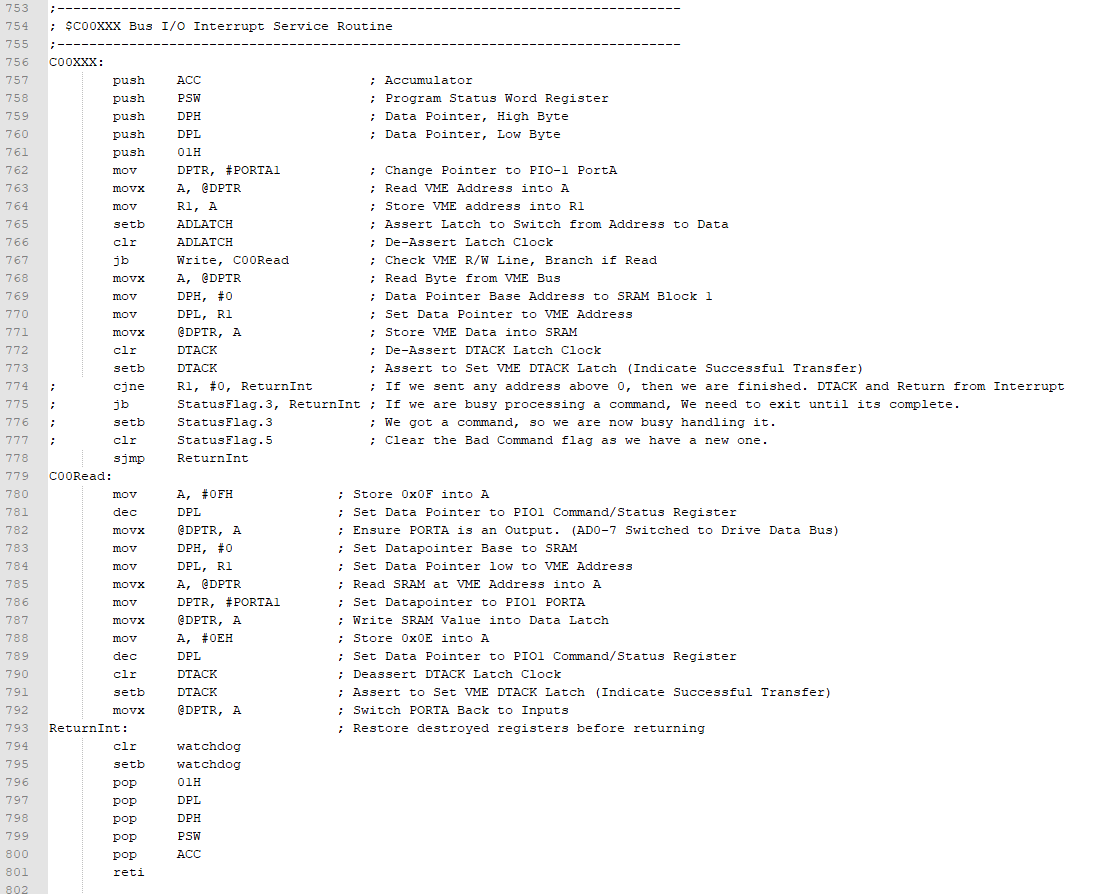

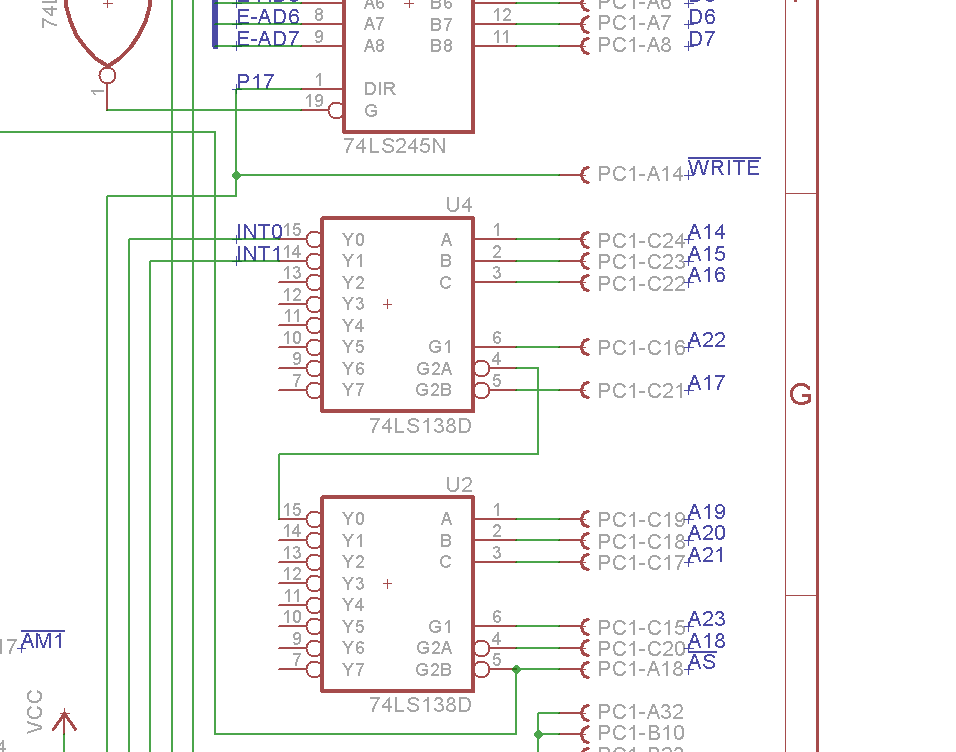

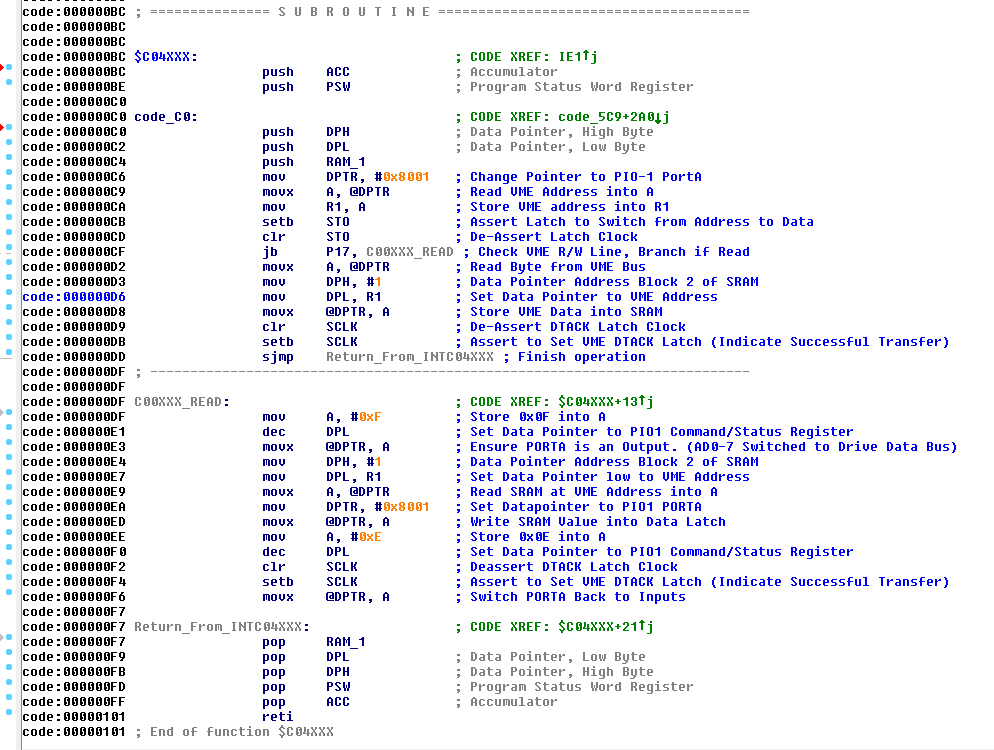

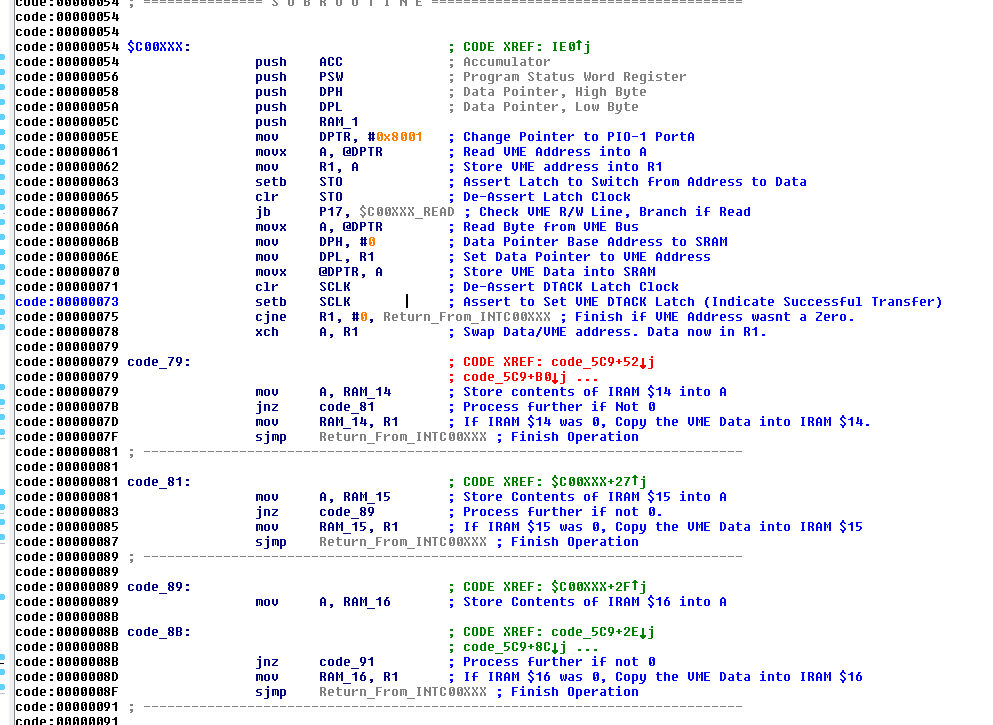

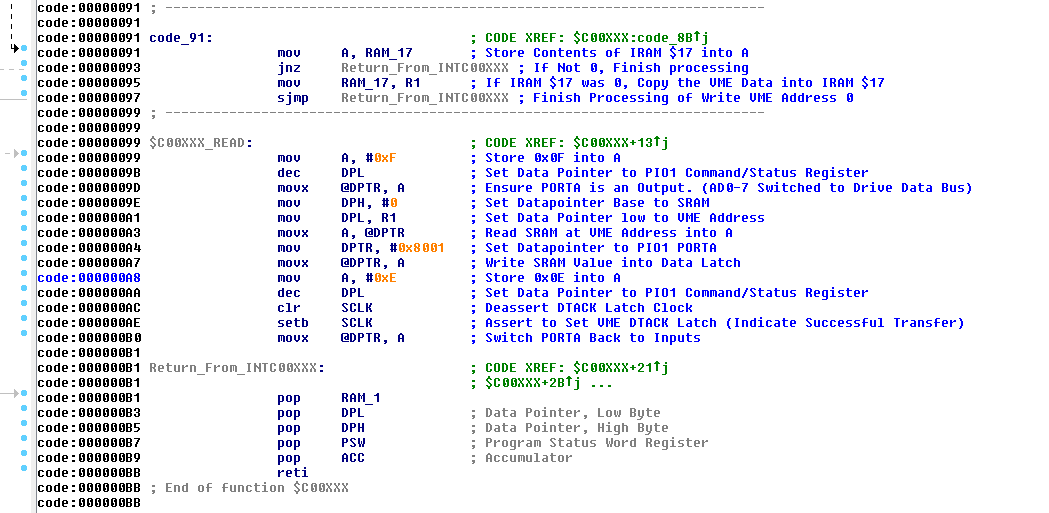

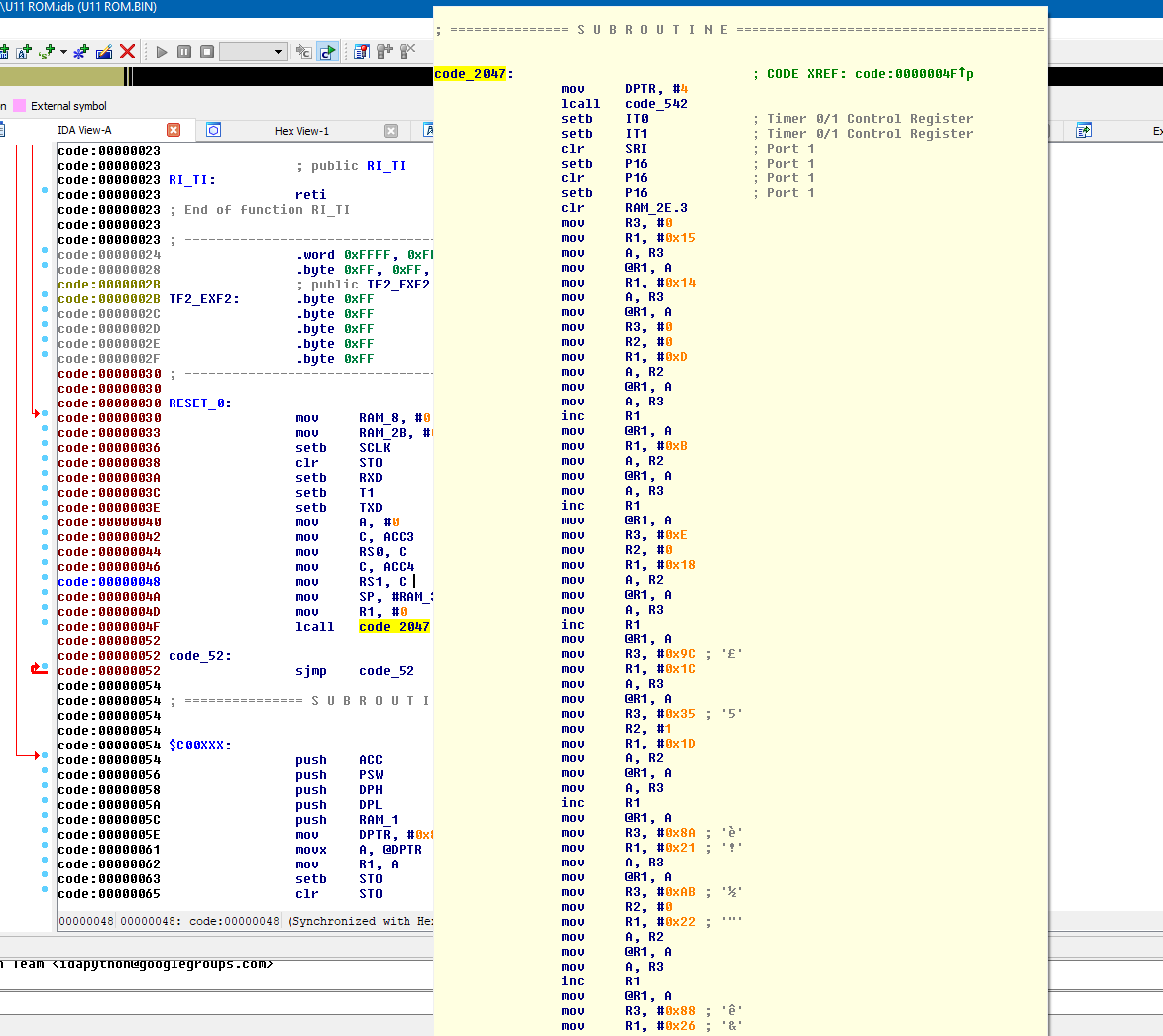

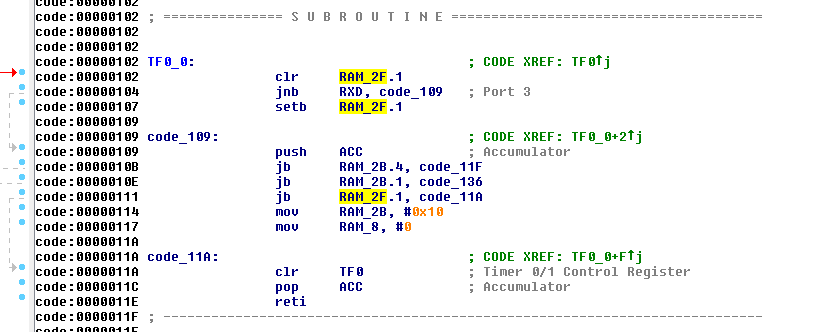

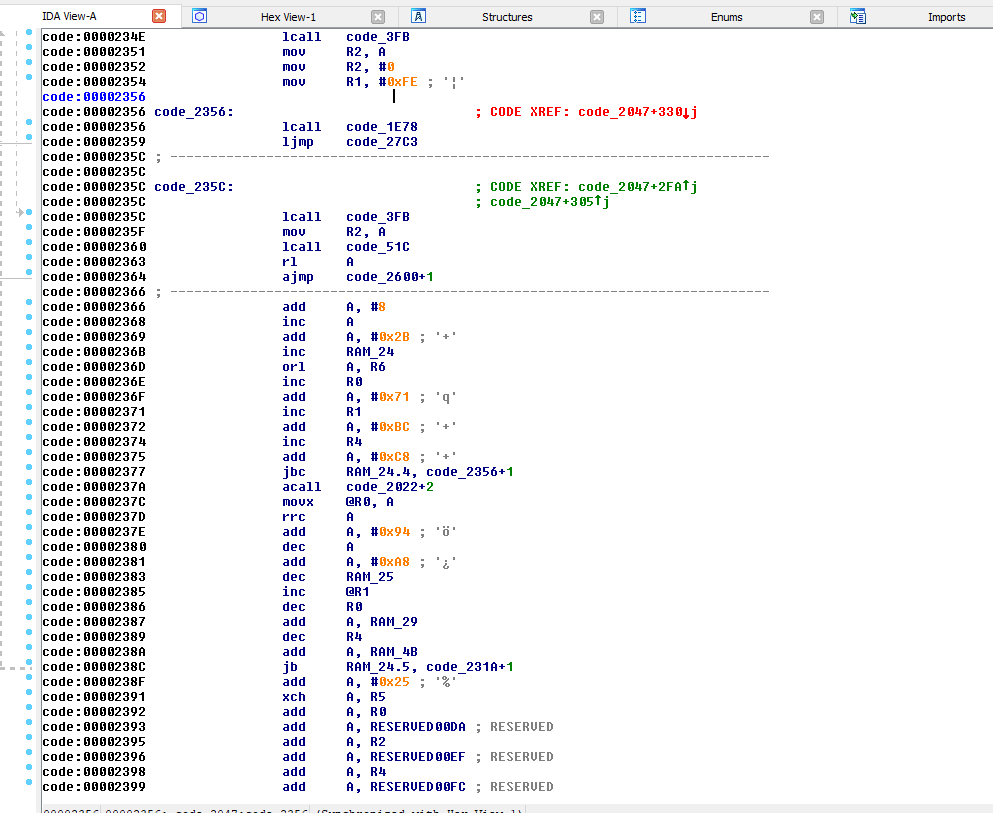

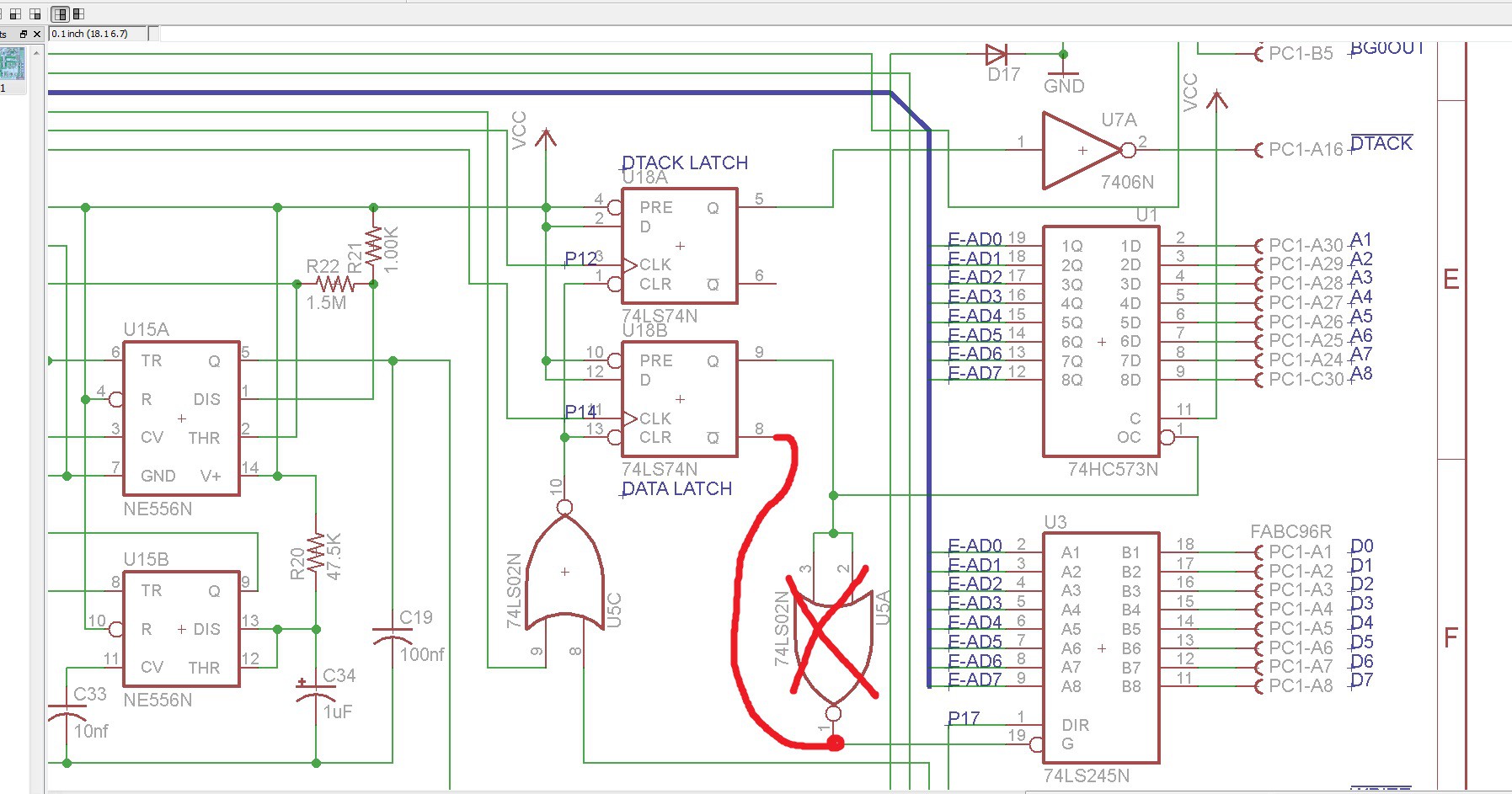

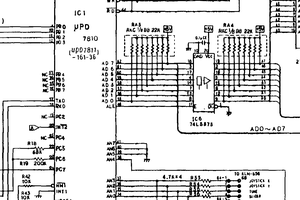

Reverse Engineering The Weather STAR 4000

The Weather STAR 4000: A Journey of reverse engineering the hardware to an iconic machine of the 1980s/90s.

techknight

techknight

mateusz.kolanski

mateusz.kolanski

James Ots

James Ots

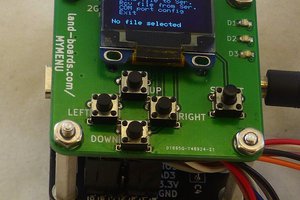

land-boards.com

land-boards.com

nice :]