My thoughts so far, WRT approach:

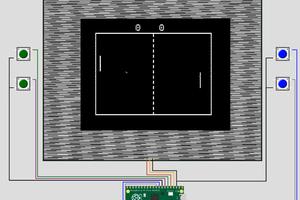

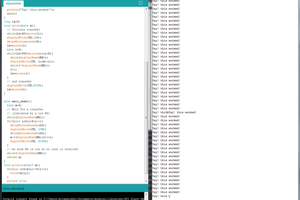

* get basic clock and data output working using SPI or APA102 as an example

* setup a clock that is a multiple of the short sync signal working with an argument of how many cycles to be low

* work on a cycle of long/short syncs for the equalizing and vertical sync pulse(s)

* add back porch and hsync

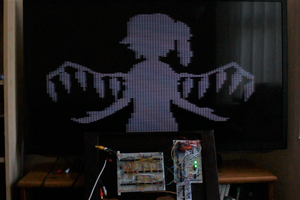

* add image data for basic bloop/dot/rectangle/all white screen

All of that should happen in the PIO independent of the C code, the final step for PAL/NTSC support should be adding the ability to spoot out image data from the input FIFO, in sync with the sync pulses.

Stretch goals once the basic game works would be:

* DMA for image data

* set up a 'latch-able' image buffer/double buffer

* figure out how to separate the sync output and data output from different state machines - why?

* use the second PIO to read input from rotary encoders or possibly pots w/ ADCs

* basic synth for music and bloops

* All of the above should have decent c/"engine" support

* better graphics/menus/music, etc.

siddacious

siddacious

Uri Shaked

Uri Shaked

Kurt Kiefer

Kurt Kiefer

Dylan Brophy

Dylan Brophy