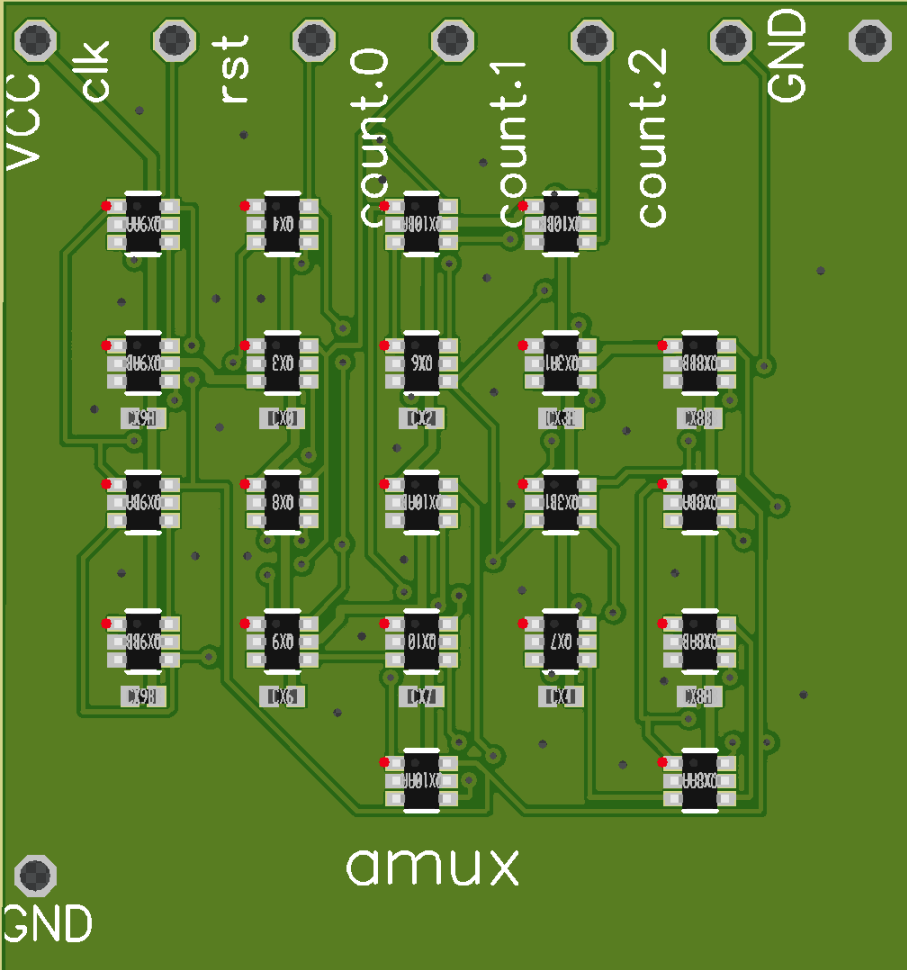

Next try at analog multiplexer logic: In addition to fixing the bug in the latch, I also added a few optimizations to the logic style: DFF are now taking only 4 amux and I introduced a few additional gate types (ANDN2, ORN2) that helped to reduced logic complexity. As a result, the counter now only takes 21 amux ICs, instead of 26 before. Furthermore, decoupling capacitors are automotically inserted now.

Pure AMUX logic

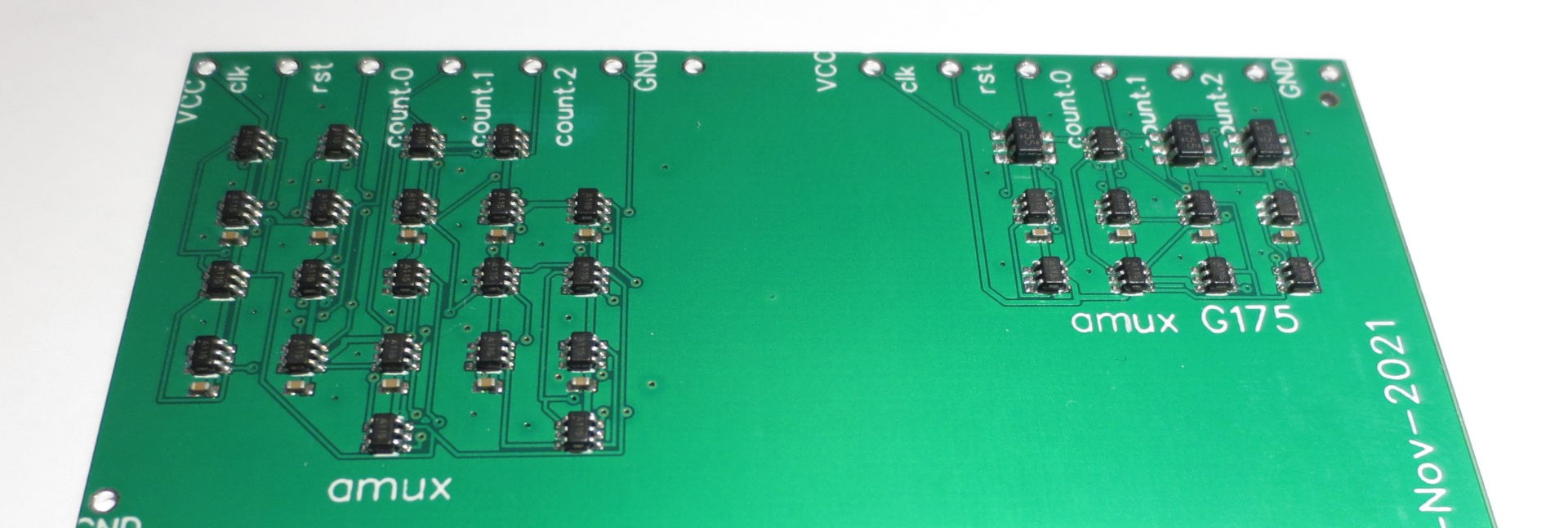

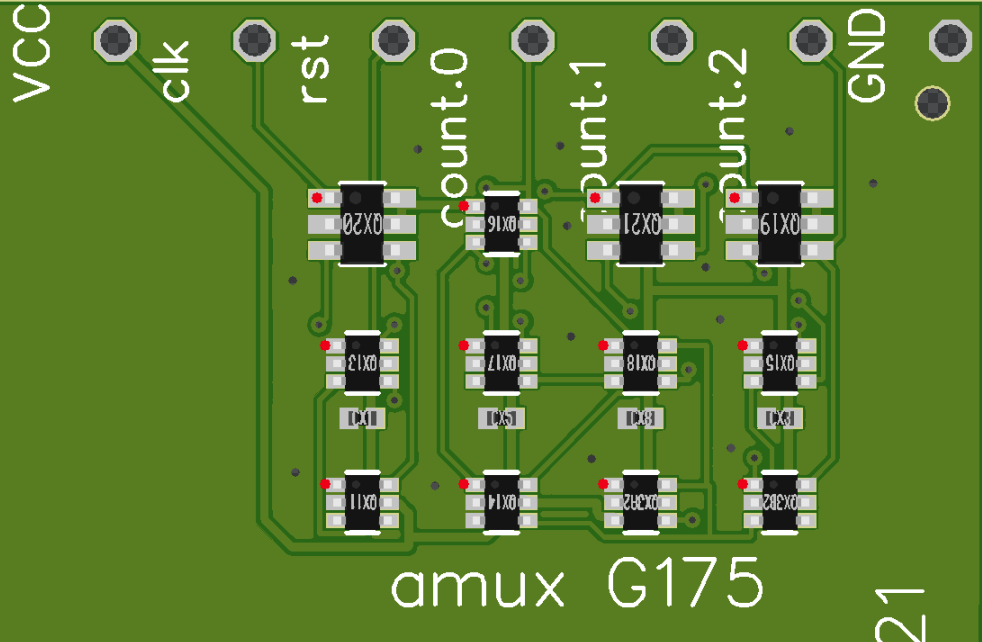

The pcb layout is shown above. The PCB is shared with a few other designs to save on PCB cost.

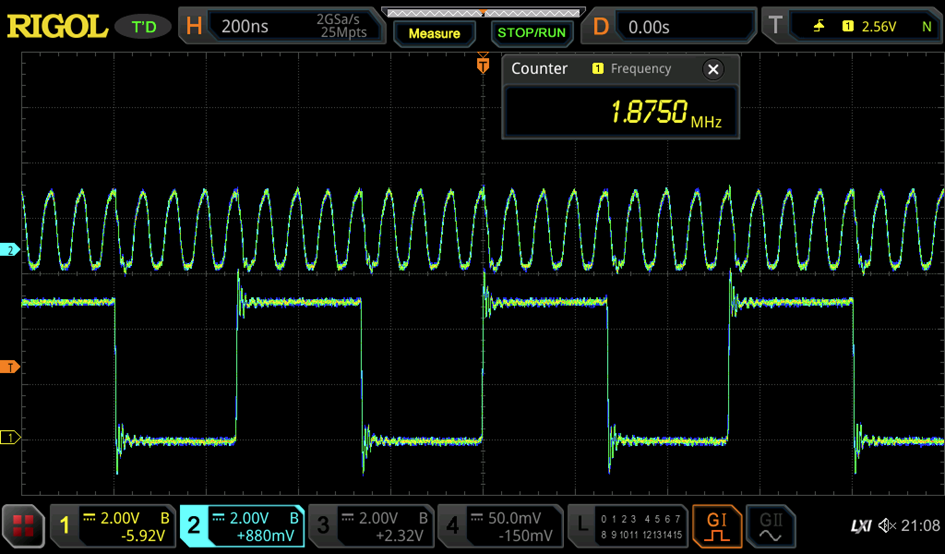

This time, the design works perfectly. Thanks to the fast analog multiplexers, it operates up very high clock speed.

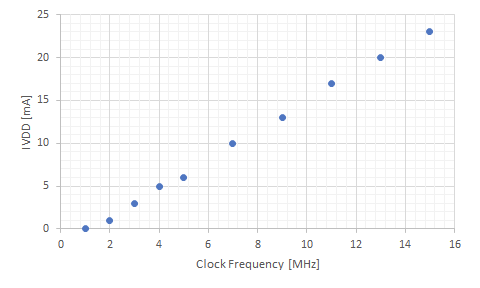

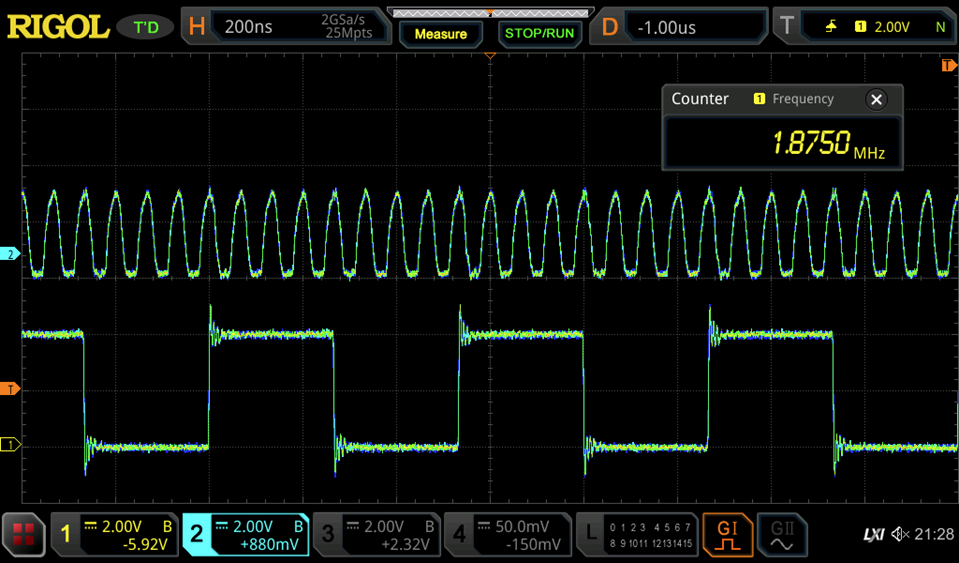

The scope trace shows operation of the counterat an input frequency of 15 MHz, the highest I can generate with the generator. The output of the third bit is toggled at 1.875MHz (15/8). No doubt, there is still a upside. The amux gates are contructed in a way, where they don't draw static power without an applied clock. Current is only consumed during switching, as in CMOS logic. (In fact, the analog switches are basically CMOS pass gates).

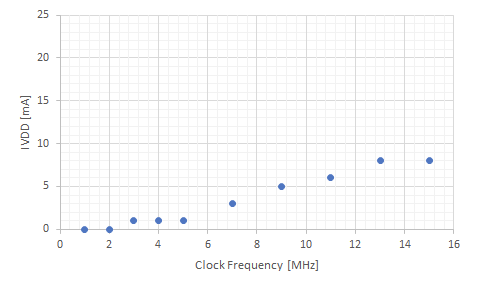

As a consequence, the current consumption is proportional to the clock frequency, as shown above.

AMUX/G175 logic

While the analog multiplexers are very efficient in realizing most simple combinatoric gates with only one component, forming a D-Flipflop still takes 4. It is more cost efficient to use a single gate D-Flipflip (74LCV1G175) instead. This allows realizing and digital circuit out of only two component types.

Only 12 ICs are required now, down from 21.

Not surprisingly, also this logic style is easily able to be clocked at 15 MHz. Assumingly even higher clock frequencies than with pure amux logic are possible. The 74LVC1G175 D-Flipflop alone can be clocked at more than 200MHz according to the datasheet.

One issue I observed was significant glitching for VDD=5V. Only at VDD=4.5V and lower stable operation was observed. Presumably, overshoot generated by the amux gates is creating issues at marginal operating voltage.

Current consumption is about half of that of the pure amux logic.Obviously, because of the lower current consumption of the 1G175 vs. the discrete amux implementation.

Summary

Amux logic works nicely now, resulting in very small designs and extremely fast logic. Unless discrete transistor logic is desired, amux logic+1G175 is probably the best style to use for more complex designs.

Tim

Tim

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.