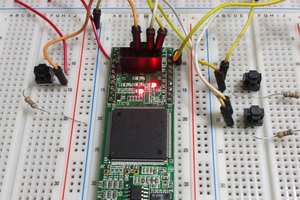

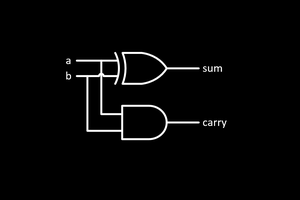

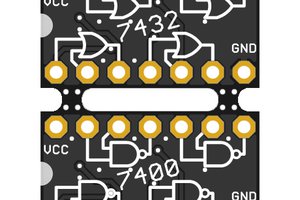

During reading about rp2040 architecture and possibilities opened by PIO I started wondering about making hobby grade logic analyser that would be supported by sigrok. What I found was that i.e. someone already tested SUMP library on pico (see links) and initial potential was already discovered: 8 channels, 125Mhz sampling, 65k samples. Pretty good for a start. After that I started digging around how logic analysers are usually built. Seeing two other great projects (Beagle logic standalone and Logic pirate) I aimed that for rpi it would be best to go with following: buffer or some double bus shifting device, possibly some RC and diodes for additional protection and triggered SRAM modules that would sample inputs (pretty much like the bus pirate does this). After sampling is complete rpi would start downloading and streaming samples to host PC via i.e. USB and extended SUMP. It came to my mind that wifi would be convenient addition. The same goes for adding some signal generator if there are still resources left (pins, cores). This project aims to be a help for hobbyists and students and open source community in general to have affordable capable logic analyser without using some clones/ fakes. I think pico will make it possible.

Since I am a software engineer and my HW knowledge is limited I need to consult my concept given above with HW magicians. My concerns are:

- what would be reasonable input conditioning (considering price and usability) and level shifting capabilities

- would I need to add RC and diodes to protect against overcurrent and ESD beside what input buffer IC would withstand

- would layout need to be somehow specifically designed to counter channel cross talk for assumed 100Mhz signals?

If You have some experience in it drop me a comment :)

J-Wrobel

J-Wrobel

Al Williams

Al Williams

Luke Valenty

Luke Valenty

patrick.revol

patrick.revol

JRodrigo

JRodrigo