I'm aware of many issues with my collection. I've been informed that not every is attributable to ETI, for example the Forth manual was written by Eric Lindsay directly for Applix. I should probably file the lot under the com/Applix directory, and say which ones were published in ETI.

Note that I am not here to pass off other people's work as my own, but merely to OCR and re-typeset material in html format, freeing them from obsolete Desktop Publishing software.

I only made a start on the Forth manual, because it is not a very popular language and does not merit spending much time on it. It is not top-priority hobby work because 1616 enthusiasts are a minority.

I can't actually host the html on hackaday so I'm more than happy for the copyright owners to do so.

| have been buried in paid work until recently, but am happy to comply with copyright holders' wishes.

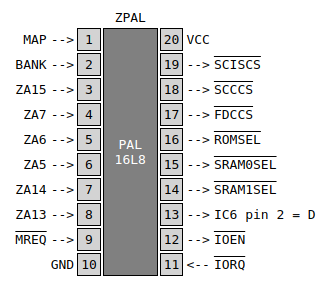

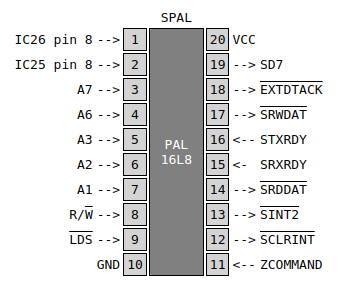

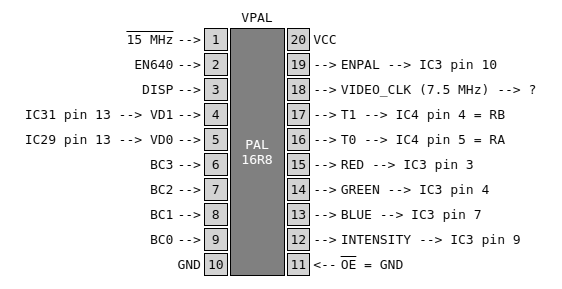

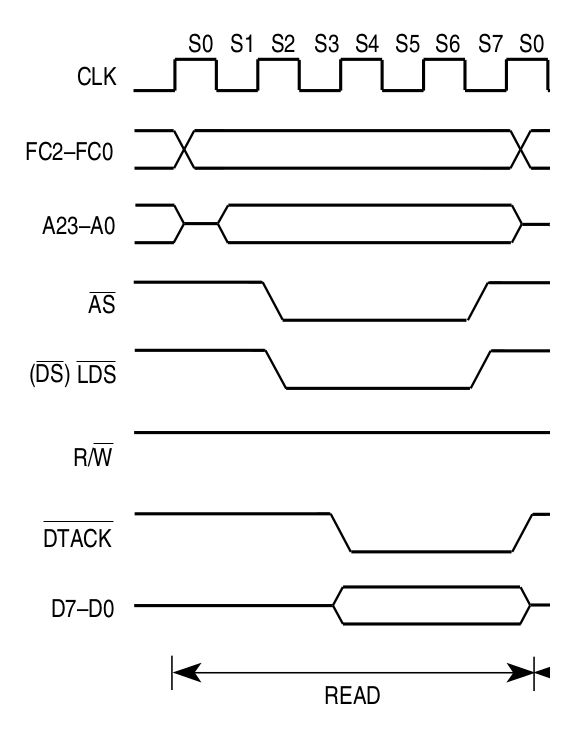

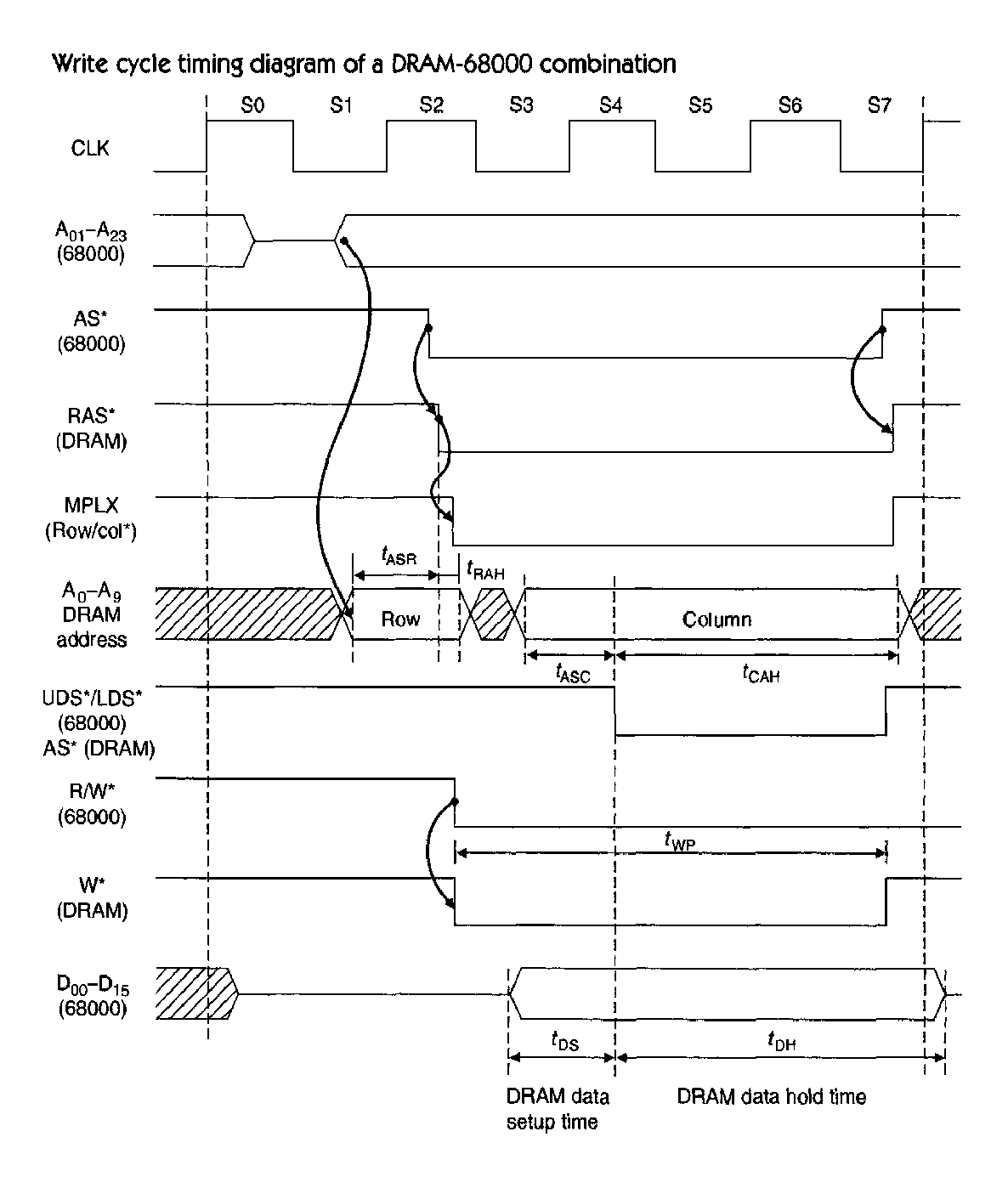

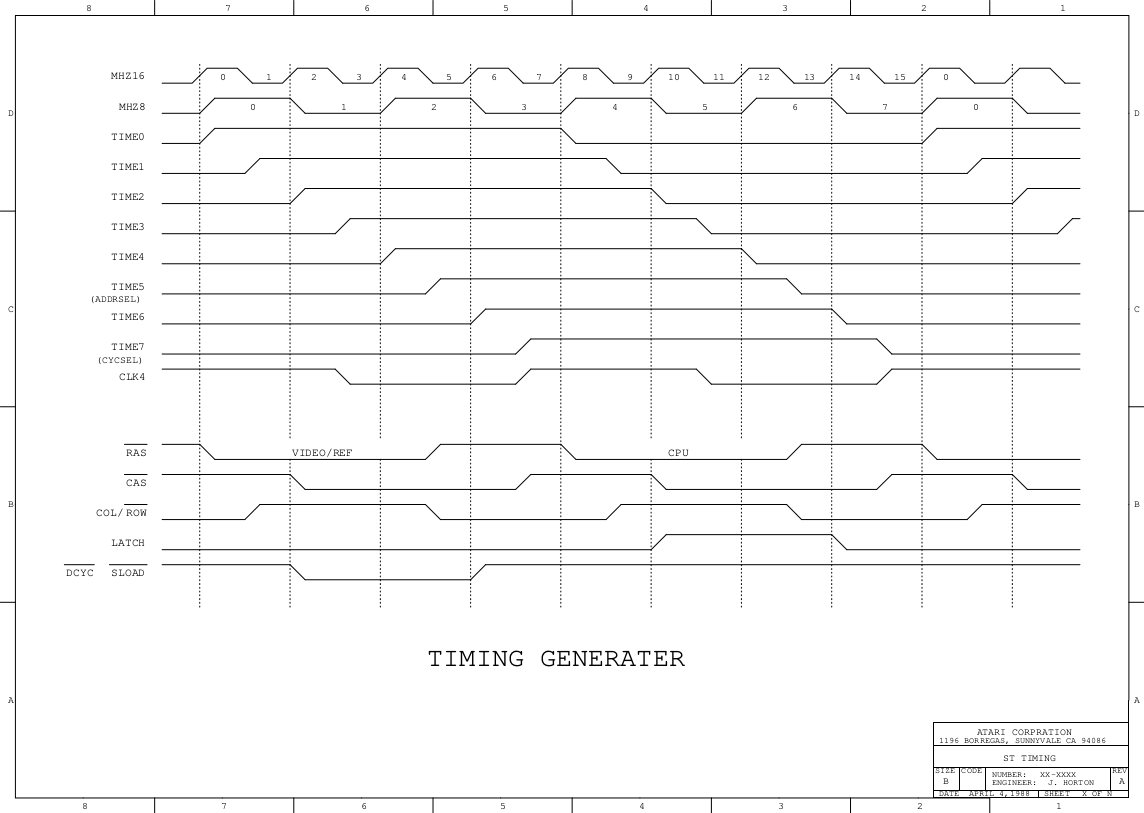

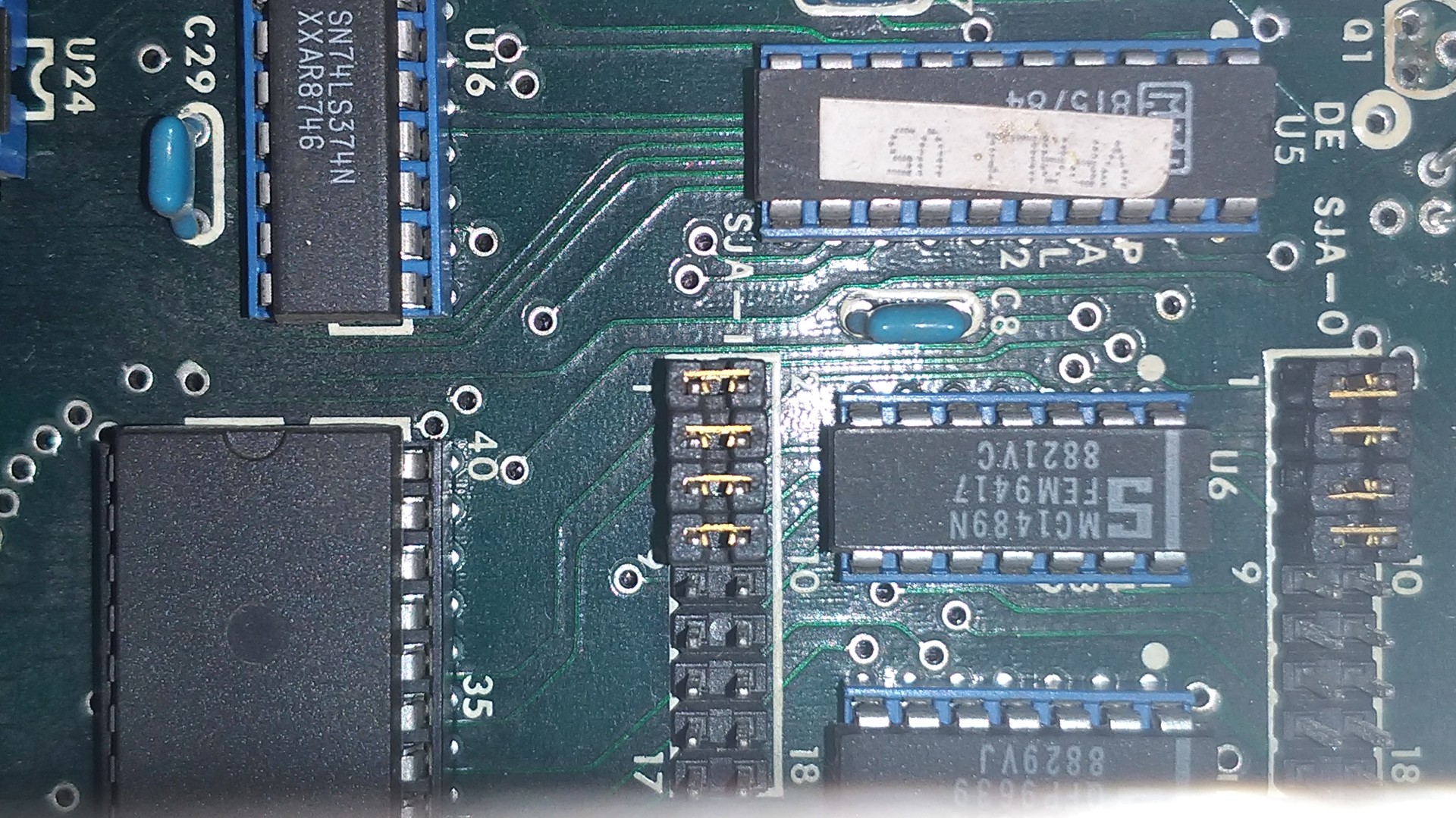

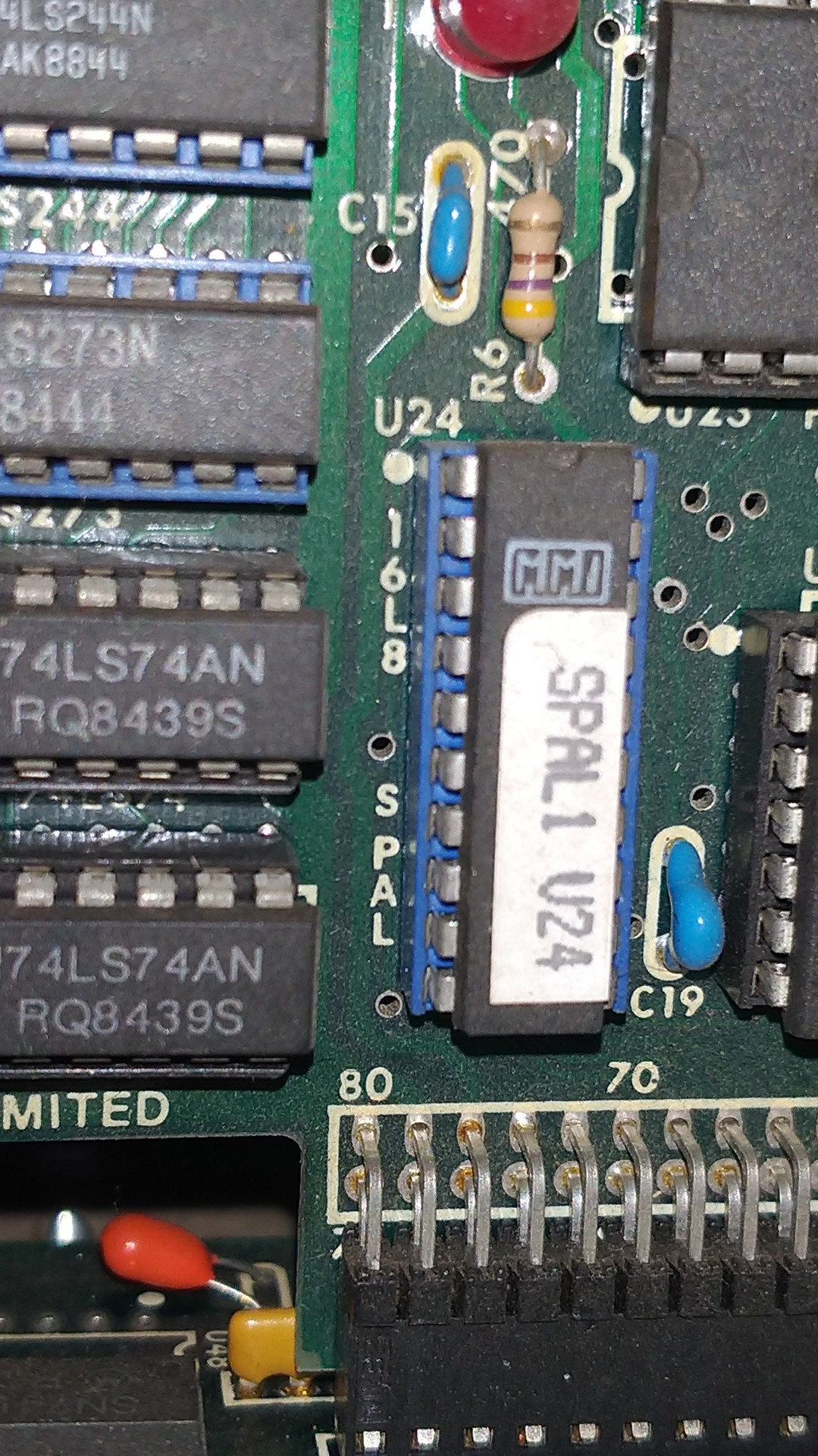

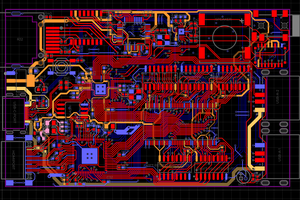

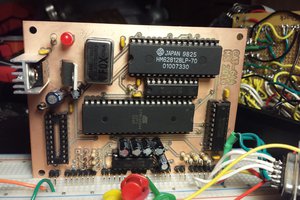

Recreating the PAL devices is my main concern, as they are the only obstacle to recreating the 1616 completely. I have the timing diagrams of an Atari machine, which is a good starting point. Without any information or access to the 1616 chips or waveforms, it is impractical to try cloning them. However, I thought it might be possible to make a primitive 1616 circuit that is just a 68000 (or 68008) chip that runs a loop generating video access DRAM cycles. I have some spare CPUs in my collection. Alternatively I could try creating a model in FPGA.

Keith

Keith

TEC.IST

TEC.IST

6502Nerd

6502Nerd

Mars

Mars