512KB 55ns SRAM added

512KB ROM added

MC68901 Multifunction Peripheral added

The CPLD at the top is a 7ns part and is tasked with address decoding and chip select generation. The CPLD on the lower right is handling the VMEbus signal synthesis and is additionally dealing with the interrupt signals.

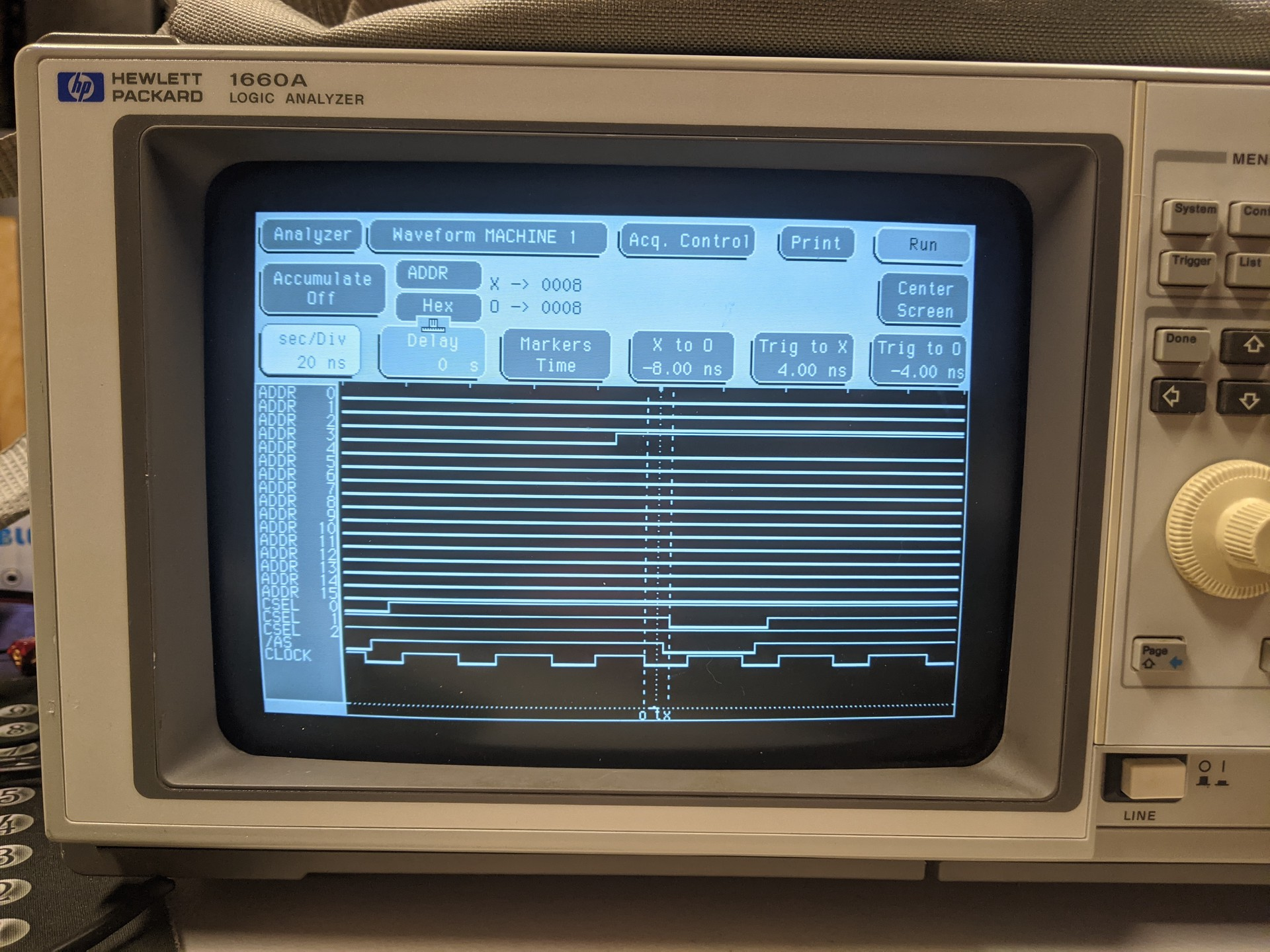

Initially I had concern that the CPLD would not be fast enough for address decoding, but it seems to be doing the job. My logic analyzer only runs up to 500MHz, so 2ns is my resolution, but the CPLD is driving the chip select low within 2ns of the address strobe being asserted.

In this capture, ADDR3 through ADDR 15 is attached to A19 through A31 on the CPU. CSEL 0 is ROM and CSEL 1 is the MFP chip select. As expected, the CPU transitioned from asserting ROMCS to asserting MFPCS when A19 went high. The time between /AS being asserted and MFPCS being asserted was within 2ns. The only think keeping me from running this thing at 0-waitstate is the fact that my pokey SRAM is only 55ns. I have faster parts on hand, but i will need to make a PCB for those as they are surfacemount components.

Jason Westervelt

Jason Westervelt

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.